## RICE UNIVERSITY

# Efficient Optimization of Memory Accesses in Parallel Programs

by

# Rajkishore Barik

A THESIS SUBMITTED

IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE

# **Doctor of Philosophy**

APPROVED, THESIS COMMITTEE:

Vivek Sarkar, Chair E.D. Butcher Professor of Computer Science

Keith Cooper L. John and Ann H. Doerr Professor of Computer Science

Timothy Harvey Research Scientist Dept. of Computer Science

Lin Zhong Assistant Professor Dept. of Electrical Engineering & Computer Science

Houston, Texas October, 2009

#### **ABSTRACT**

# Efficient Optimization of Memory Accesses in Parallel Programs

by

## Rajkishore Barik

The power, frequency, and memory wall problems have caused a major shift in mainstream computing by introducing processors that contain multiple low power cores. As multi-core processors are becoming ubiquitous, software trends in both parallel programming languages and dynamic compilation have added new challenges to program compilation for multi-core processors. This thesis proposes a combination of high-level and low-level compiler optimizations to address these challenges.

The high-level optimizations introduced in this thesis include new approaches to May-Happen-in-Parallel analysis and Side-Effect analysis for parallel programs and a novel parallelism-aware Scalar Replacement for Load Elimination transformation. A new Isolation Consistency (IC) memory model is described that permits several scalar replacement transformation opportunities compared to many existing memory models.

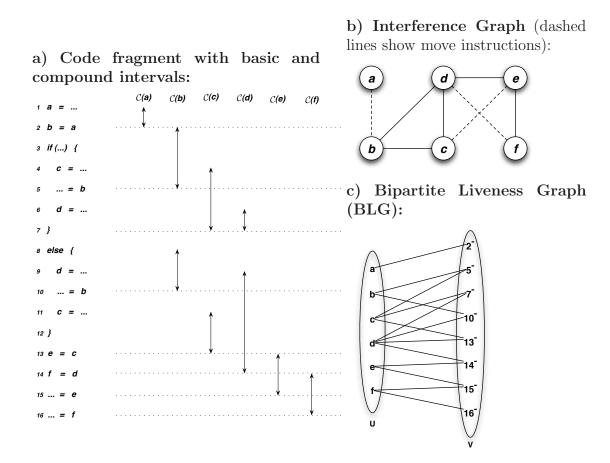

The low-level optimizations include a novel approach to register allocation that retains the compile time and space efficiency of Linear Scan, while delivering runtime performance superior to both Linear Scan and Graph Coloring. The *allocation* phase is modeled as an optimization problem on a Bipartite Liveness Graph (BLG) data structure. The *assignment* phase focuses on reducing the number of spill instructions by using register-to-register move and exchange instructions wherever possible.

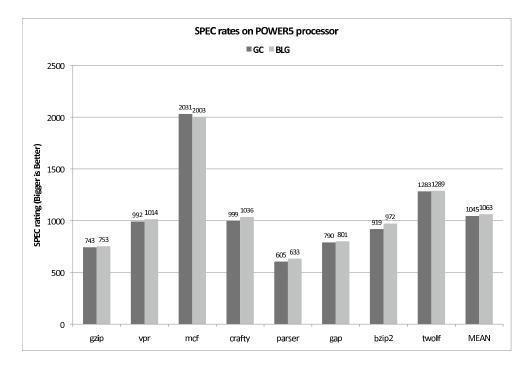

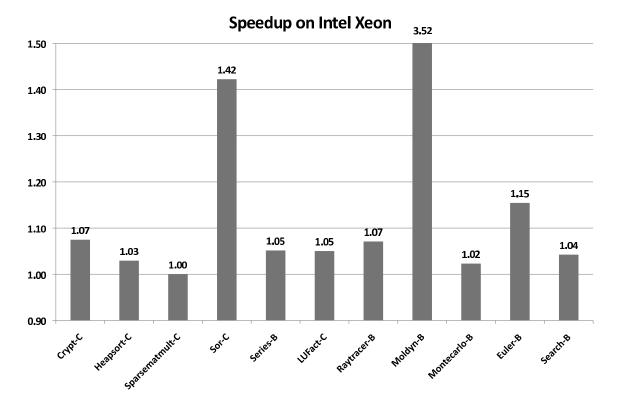

Experimental evaluations of our scalar replacement for load elimination transformation in the Jikes RVM dynamic compiler show decreases in dynamic counts for getfield operations of up to 99.99%, and performance improvements of up to 1.76× on 1 core, and 1.39× on 16 cores, when compared with the load elimination algorithm available in Jikes RVM. A prototype implementation of our BLG register allocator in Jikes RVM demonstrates runtime performance improvements of up to 3.52× relative to Linear Scan on an x86 processor. When compared to Graph Coloring register allocator in the GCC compiler framework, our allocator resulted in an execution time improvement of up to 5.8%, with an average improvement of 2.3% on a POWER5 processor.

With the experimental evaluations combined with the foundations presented in this thesis, we believe that the proposed high-level and low-level optimizations are useful in addressing some of the new challenges emerging in the optimization of parallel programs for multi-core architectures.

# Acknowledgments

I would like to express my appreciation to my thesis committee, especially to my adviser, Prof. Vivek Sarkar, for his patient guidance and support. He is always full of energy and enthusiasm for attacking research problems and possesses one of the sharper brains. The door to his office was always open whenever I ran into a trouble spot in both academically and personally. And during the most difficult times when writing this thesis, he gave me the moral support and the freedom I needed to move on. It was an honor to work with him. I owe my deepest gratitude to my thesis co-chair Prof. Keith D. Cooper for his technical advice during the course work of COMP 512 that went onto play an important role in my thesis work. I am grateful to my thesis co-chair Dr. Timothy J. Harvey for his guidance on register allocation and his useful suggestions and advice that significantly helped improving the presentation of this thesis. There are several people at Rice University that helped me during my graduate career including Prof. Lin Zhong, David Peixotto, Jisheng Zhao, Jun Shirako, Yi Guo, Raghavan Raman, and Prof. John Mellor-Crummey.

I had the privilege to work under Prof. Thomas Gross, my advisor at ETH, Zurich. His guidance and support has been invaluable during my early graduate school days. I also recognize the enormous amount of help provided by Dr. Christoph von Praun on clarifying my innumerable doubts on ERCO infrastructure at ETH.

This thesis would not have been possible without support from my managers at IBM who allowed me to pursue Ph.D. while being a full-time employee. I would like to thank my managers at IBM including Dr. Ravi Kothari, Dr. Sugata Ghosal, Dr. R. K. Shyamasundar, Dr. Calin Cascaval, Dr. Rahul Garg, and Dr. Vijay Saraswat. It has been enjoyable experience working with them. I would like to thank

all members of the X10 team at IBM for valuable discussions and feedback related to this thesis work, especially Igor Peshansky for discussion of the semantics of Java final variables. I am thankful to all X10 team members for their contributions to the X10 software used in this thesis. I gratefully acknowledge the support from an IBM Open Collaborative Faculty Award. This work was supported in part by the National Science Foundation under the HECURA program, award number CCF-0833166.

I would like to acknowledge my collaborators Shivali Agarwal and Prof. R. K. Shyamasundar from TIFR. The work on May-Happens-in-Parallel (MHP) analysis in Chapter 3 was done with their collaboration. I would also like to thank IBM Summer intern, Puneet Goyal, for his work on bitwidth-aware packing that led to our work in Chapter 7.

Finally, I gratefully acknowledge my family's love and encouragement. My beloved wife, Meena, has been a constant source of inspiration during the rough times of graduate life. Her patience, love and encouragement have upheld me, particularly in those many days in which I spent more time with computer than with her. I dedicate my thesis to her. I owe my deepest gratitude to my IBM colleague and close friend, Rema Ananthanarayan, for motivating me to come to Rice and for helping me personally.

# Contents

|                       | Abs  | tract                                                  | i  |  |

|-----------------------|------|--------------------------------------------------------|----|--|

| Acknowledgments       |      |                                                        |    |  |

| List of Illustrations |      |                                                        |    |  |

|                       | List | of Tables                                              | X  |  |

| 1                     | Int  | roduction                                              | 1  |  |

|                       | 1.1  | Research Contributions                                 | ۷  |  |

|                       | 1.2  | Thesis Organization                                    | (  |  |

| <b>2</b>              | Ba   | ckground                                               | 7  |  |

|                       | 2.1  | Basics of a Compiler                                   | ,  |  |

|                       | 2.2  | The HJ Parallel Programming Language                   | 1  |  |

|                       |      | 2.2.1 Single Place HJ Language Constructs              | 1: |  |

|                       |      | 2.2.2 Multi-Place Programming in HJ                    | 10 |  |

|                       |      | 2.2.2.1 Remote Asyncs                                  | 18 |  |

|                       | 2.3  | Code Optimization Framework                            | 19 |  |

|                       | 2.4  | May-Happen-in-Parallel ( $MHP$ ) Analysis              | 2  |  |

|                       |      | 2.4.1 MHP Analysis for Java Programs                   | 23 |  |

|                       | 2.5  | Side-Effect Analysis                                   | 2' |  |

|                       | 2.6  | Scalar Replacement Transformation for Load Elimination | 3  |  |

|                       |      | 2.6.1 Unified Modeling of Arrays and Objects           | 33 |  |

|                       |      | 2.6.2 Extended Array SSA form                          | 34 |  |

|                       |      | 2.6.3 Load Elimination Algorithm                       | 3  |  |

|                       | 2.7  | Register Allocation                                    | 30 |  |

|   |     | 2.7.1  | Terminology                                          | 37 |

|---|-----|--------|------------------------------------------------------|----|

|   |     |        | 2.7.1.1 Liveness, Live-ranges and Interference Graph | 37 |

|   |     |        | 2.7.1.2 Spilling                                     | 38 |

|   |     |        | 2.7.1.3 Coalescing                                   | 38 |

|   |     |        | 2.7.1.4 Live-range splitting                         | 39 |

|   |     |        | 2.7.1.5 Architectural Considerations                 | 39 |

|   |     | 2.7.2  | Register Allocation Techniques                       | 40 |

|   |     |        | 2.7.2.1 Graph Coloring Register Allocation           | 40 |

|   |     |        | 2.7.2.2 Linear Scan Register Allocation              | 43 |

|   |     |        | 2.7.2.3 SSA-based Register Allocation                | 50 |

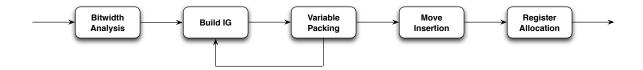

|   | 2.8 | Bitwic | lth-aware Register Allocation                        | 52 |

|   |     | 2.8.1  | Bitwidth Analysis                                    | 55 |

|   |     | 2.8.2  | Variable Packing                                     | 56 |

|   |     | 2.8.3  | Move Insertion                                       | 58 |

|   |     | 2.8.4  | Register Allocation                                  | 59 |

| 3 | Ma  | y-Ha   | ppen-in-Parallel (MHP) Analysis                      | 60 |

|   | 3.1 |        |                                                      | 60 |

|   | 3.2 | Steps  | for MHP analysis of HJ programs                      | 61 |

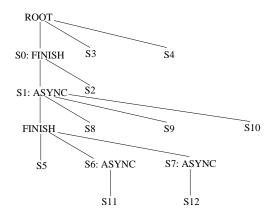

|   | 3.3 | Progra | am Structure Tree ( <i>PST</i> ) Representation      | 62 |

|   |     | 3.3.1  | Example                                              | 63 |

|   | 3.4 | Never- | Execute-in-Parallel Analysis                         | 65 |

|   |     | 3.4.1  | Comparison with MHP Analysis of Java programs        | 67 |

|   |     | 3.4.2  | Complexity                                           | 74 |

|   |     | 3.4.3  | Example                                              | 74 |

|   | 3.5 | Place  | Equivalence Analysis                                 | 76 |

|   |     | 3.5.1  | Complexity                                           | 81 |

|   |     | 3.5.2  | Example                                              | 81 |

|   |                      |                                                     |                                                  | viii |  |  |

|---|----------------------|-----------------------------------------------------|--------------------------------------------------|------|--|--|

|   | 3.6                  | МНР                                                 | Analysis using Isolated Sections                 | 81   |  |  |

|   |                      | 3.6.1                                               | Complexity                                       | 83   |  |  |

|   |                      | 3.6.2                                               | Example                                          | 83   |  |  |

|   | 3.7                  | Summ                                                | nary                                             | 84   |  |  |

| 4 | $\operatorname{Sid}$ | e-Effe                                              | ect Analysis for Parallel Programs               | 85   |  |  |

|   | 4.1                  | Side-E                                              | Effect Analysis of Method Calls                  | 86   |  |  |

|   |                      | 4.1.1                                               | Heap Array Representation                        | 88   |  |  |

|   |                      | 4.1.2                                               | Method Level Side-effect                         | 88   |  |  |

|   |                      | 4.1.3                                               | Complexity                                       | 91   |  |  |

|   |                      | 4.1.4                                               | Discussion                                       | 92   |  |  |

|   | 4.2                  | Exten                                               | ded Side-effect Analysis for Parallel Constructs | 92   |  |  |

|   |                      | 4.2.1                                               | Side-Effects for Finish Scopes                   | 94   |  |  |

|   |                      | 4.2.2                                               | Side-Effects for Methods with Escaping Asyncs    | 95   |  |  |

|   |                      | 4.2.3                                               | Side-Effects for Isolated Blocks                 | 96   |  |  |

|   | 4.3                  | .3 Parallelism-aware Side-Effect Analysis Algorithm |                                                  |      |  |  |

|   |                      | 4.3.1                                               | Discussion                                       | 101  |  |  |

|   | 4.4                  | Summ                                                | nary                                             | 103  |  |  |

| 5 | Iso                  | lation                                              | n Consistency Memory Model and its Impact on     | ,    |  |  |

| J |                      |                                                     |                                                  |      |  |  |

|   |                      |                                                     | 1                                                | 105  |  |  |

|   | 5.1                  | Progra                                              | am Transformation and Memory Model               | 105  |  |  |

|   | 5.2                  | Isolati                                             | Ion Consistency Memory Model                     | 108  |  |  |

|   |                      | 5.2.1                                               | Abstraction                                      | 109  |  |  |

|   |                      | 5.2.2                                               | State-Update rules for $L$                       | 110  |  |  |

|   |                      | 5.2.3                                               | State Observability for $L$                      | 112  |  |  |

|   |                      | 5.2.4                                               | Example Scenarios                                | 113  |  |  |

|   | 5.3                  | Scalar                                              | Replacement for Load Elimination                 | 115  |  |  |

|   |     | 5.3.1 Example                                            | 117 |

|---|-----|----------------------------------------------------------|-----|

|   | 5.4 | Summary                                                  | 117 |

| 6 | Spa | ace-Efficient Register Allocation                        | 120 |

|   | 6.1 | Notions Revisited                                        | 121 |

|   | 6.2 | Example                                                  | 123 |

|   | 6.3 | Overall Approach                                         | 126 |

|   | 6.4 | Allocation using Bipartite Liveness Graphs               | 129 |

|   |     | 6.4.1 Eager Heuristic                                    | 132 |

|   | 6.5 | Assignment using Register Moves and Exchanges            | 134 |

|   |     | 6.5.1 Spill-Free Assignment                              | 134 |

|   |     | 6.5.2 Example                                            | 138 |

|   |     | 6.5.3 Assignment with Move Coalescing and Register Moves | 140 |

|   | 6.6 | Allocation and Assignment with Register Classes          | 143 |

|   |     | 6.6.1 Constrained Allocation using <i>BLG</i>            | 145 |

|   |     | 6.6.2 Constrained Assignment                             | 145 |

|   | 6.7 | Extended Linear Scan (ELS)                               | 149 |

|   | 6.8 | Summary                                                  | 150 |

| 7 | Bit | width-aware Register Allocation                          | 152 |

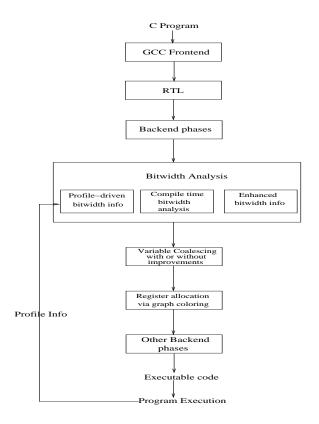

|   | 7.1 | Overall Bitwidth-aware register allocation               | 153 |

|   | 7.2 | Limit Study                                              | 153 |

|   | 7.3 | Enhanced Bitwidth Analysis                               | 156 |

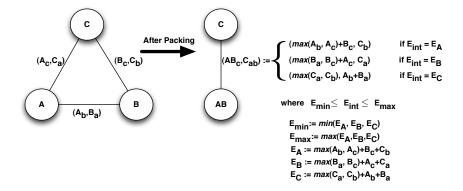

|   | 7.4 | Enhanced Packing                                         | 160 |

|   |     | 7.4.1 Improved <i>EMIW</i> estimates                     | 164 |

|   | 7.5 | Summary                                                  | 164 |

| 8 | Per | rformance Results                                        | 166 |

|   | 8.1 | Side-Effect Analysis and Load Elimination                | 166 |

|   |               | 8.1.1  | Experim   | ental setup           | 166 |

|---|---------------|--------|-----------|-----------------------|-----|

|   |               | 8.1.2  | Experim   | nental results        | 168 |

|   | 8.2           | Space- | Efficient | Register Allocation   | 176 |

|   |               | 8.2.1  | GCC Ev    | valuation             | 176 |

|   |               |        | 8.2.1.1   | Experimental setup    | 176 |

|   |               |        | 8.2.1.2   | Experimental results  | 178 |

|   |               | 8.2.2  | Jikes RV  | M evaluation          | 179 |

|   |               |        | 8.2.2.1   | Experimental setup    | 179 |

|   |               |        | 8.2.2.2   | Experimental results  | 180 |

|   | 8.3           | Bitwic | lth-Aware | e Register Allocation | 182 |

|   |               | 8.3.1  | Experim   | nental setup          | 182 |

|   |               | 8.3.2  | Experim   | nental results        | 183 |

|   | 8.4           | Summ   | ary       |                       | 185 |

|   |               |        |           |                       |     |

| 9 | $\mathbf{Co}$ | nclusi | ions an   | d Future Work         | 187 |

|   | 9.1           | Future | e Work .  |                       | 189 |

# Illustrations

| 2.1  | Example control flow graph (CFG)                                               | 8  |

|------|--------------------------------------------------------------------------------|----|

| 2.2  | HJ's Multi-Place Execution Model                                               | 17 |

| 2.3  | Static and Dynamic Optimization Framework                                      | 19 |

| 2.4  | CFG structures for depicting various side-effects                              | 28 |

| 2.5  | Termination of Side-effect analysis                                            | 31 |

| 2.6  | Examples of scalar replacement for load elimination transformation .           | 32 |

| 2.7  | Load elimination algorithm                                                     | 35 |

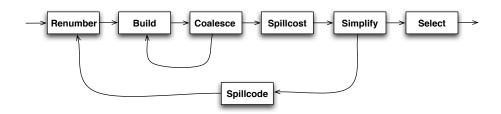

| 2.8  | Chaitin's Register Allocator                                                   | 42 |

| 2.9  | Linear Scan register allocation algorithm                                      | 47 |

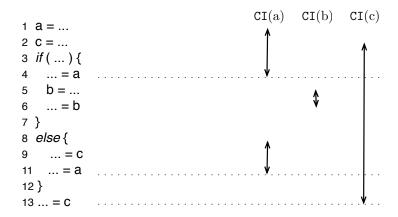

| 2.10 | Demonstration of intervals in Linear Scan register allocation                  | 48 |

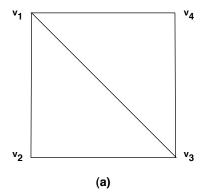

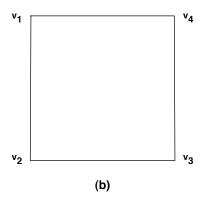

| 2.11 | Examples of chordal and non-chordal graphs                                     | 51 |

| 2.12 | SSA-based register allocation                                                  | 52 |

| 2.13 | Example code fragment demonstrating bitwidth-aware register                    |    |

|      | allocation                                                                     | 54 |

| 2.14 | Bitwidth-aware register allocation framework                                   | 54 |

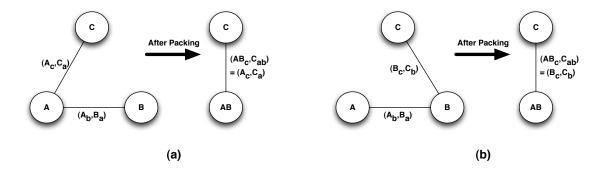

| 2.15 | Scenarios for precise variable packing using $MIW$                             | 57 |

| 2.16 | Scenario for variable packing using EMIW                                       | 58 |

|      |                                                                                |    |

| 3.1  | Example $HJ$ program to demonstrate the computation of $\mathit{MHP}(S1,S2)$ . | 64 |

| 3.2  | <i>PST</i> for example program in Figure 3.1                                   | 64 |

| 3.3  | Algorithm for computing Never-Execute-in-Parallel $(\mathit{NEP})$ relations . | 66 |

| 3.4  | Java example program to illustrate MHP algorithm                               | 67 |

4.10 Improving the precision of global *isolated* side-effects. . . . . . . . . .

104

| 5.1  | Example program illustrating violation of Sequential Consistency due                    |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | to reordering within a thread                                                           | 107 |

| 5.2  | Four parallel code fragments that demonstrate scalar replacement for                    |     |

|      | load elimination opportunities in the presence of parallel constructs. $\boldsymbol{.}$ | 114 |

| 5.3  | Parallelism-aware scalar replacement for load elimination                               |     |

|      | transformation                                                                          | 116 |

| 5.4  | Example HJ program for parallelism-aware scalar replacement                             |     |

|      | transformation                                                                          | 118 |

| 5.5  | Transformed program after scalar replacement for program shown in                       |     |

|      | Figure 5.4                                                                              | 119 |

| 6.1  | Example program for illustrating space-efficient register allocation $$                 | 123 |

| 6.2  | Example program for illustrating Space-efficient register allocation                    | 127 |

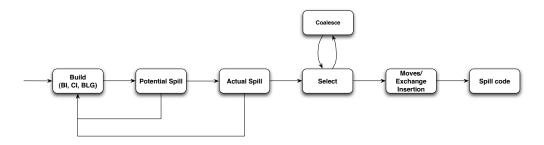

| 6.3  | Overall Space Efficient Register Allocator using $BLG$                                  | 127 |

| 6.4  | SSA based Register Allocation. This figure is adapted from [22]                         | 128 |

| 6.5  | Greedy heuristic to perform allocation using max-min strategy                           | 131 |

| 6.6  | Eager heuristic to perform allocation                                                   | 133 |

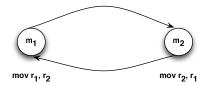

| 6.7  | Assignment using register move and exchange instructions                                | 135 |

| 6.8  | Algorithm to insert register move and exchange instructions on                          |     |

|      | control flow edges                                                                      | 137 |

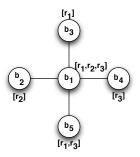

| 6.9  | Anti-dependence graph $(D)$ for the example program in Figure 6.1                       | 138 |

| 6.10 | Greedy heuristic to choose a physical register for a basic interval that                |     |

|      | maximizes copy removal                                                                  | 142 |

| 6.11 | Register classes in the Intel x86 architecture                                          | 143 |

| 6.12 | Example program demonstrating problems associated with register                         |     |

|      | assignment using register classes                                                       | 143 |

| 6.13 | Example demonstrating problems in coalescing due to register classes                    | 144 |

| 6 14 | Heuristic o perform assignment in the presence of register classes                      | 147 |

| 6.15 | Heuristic to choose a physical register that maximizes copy removal | 148 |

|------|---------------------------------------------------------------------|-----|

| 6.16 | Overview of Extended Linear Scan algorithm $(\mathit{ELS})$ with    |     |

|      | all-or-nothing approach                                             | 151 |

|      |                                                                     |     |

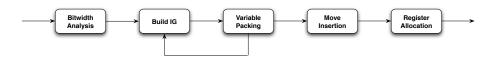

| 7.1  | Overall Bitwidth-aware register allocation framework                | 152 |

| 7.2  | GCC modification for Limit Study                                    | 154 |

| 7.3  | Recurrence analysis for bitwidth analysis                           | 158 |

| 7.4  | Code fragment from BITWISE adpcm benchmark                          | 159 |

| 7.5  | Code fragment from BITWISE bubblesort benchmark                     | 159 |

| 7.6  | Example program for demonstrating imprecision in Tallam-Gupta       |     |

|      | packing                                                             | 161 |

| 7.7  | Interference Graph for the example program shown in Figure 7.6      | 161 |

| 7.8  | Bitwidth aware register allocation in a graph coloring scenario     | 163 |

|      |                                                                     |     |

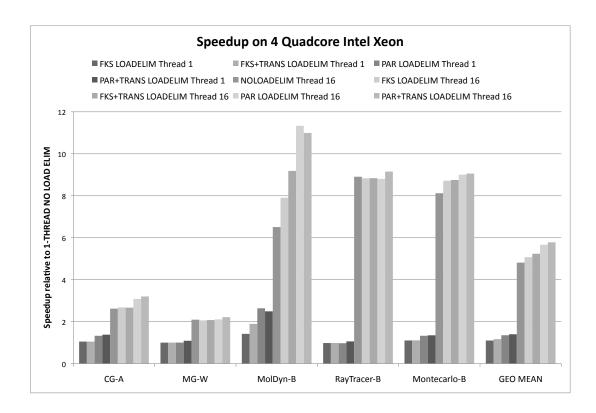

| 8.1  | Performance improvement using the scalar replacement algorithm      |     |

|      | presented in Figure 5.3                                             | 174 |

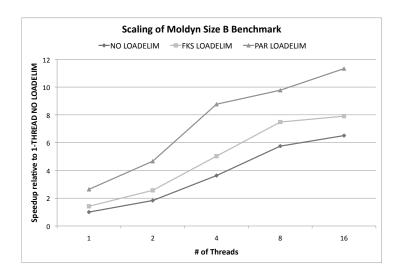

| 8.2  | Scaling of JGF Section 3 MolDyn Size B benchmark                    | 175 |

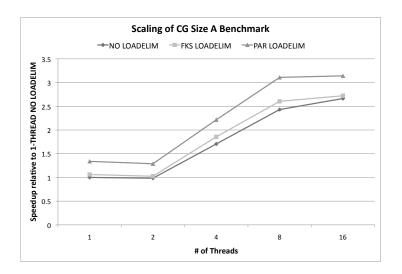

| 8.3  | Scaling of NPB CG Size A benchmark                                  | 175 |

| 8.4  | SPEC rates for Graph Coloring and ELS register Allocator described  |     |

|      | in Section 6.7                                                      | 177 |

| 8.5  | Speedup of BLG with register classes relative to LS                 | 181 |

| 8.6  | GCC modification for register allocation                            | 184 |

# Tables

| Side-effect results of parallel constructs and method calls for example |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| program shown in Figure 4.5                                             | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Comparison of SC and JMM for compile reordering transformation $$ .     | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Comparison of compile-time and profile-driven bitwidth analysis         | 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Comparison of Active Compression Factor (ACF) across static and         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| profile-driven bitwidth analysis                                        | 156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| New EMIW estimates for variable packing using NODEMAX                   | 165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Static count of parallel constructs in various benchmarks               | 168                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Compilation time in milliseconds of various benchmarks for NO           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LOADELIM, FKS LOADELIM, and FKS+TRANS LOADELIM cases.                   | 170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Compilation times in milliseconds of various benchmarks for PAR         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LOADELIM and PAR+TRANS LOADELIM cases                                   | 171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Dynamic counts of GETFIELD operations using FKS LOADELIM                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| and FKS+TRANS LOADELIM cases                                            | 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Dynamic counts of GETFIELD operations using PAR and                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PAR+TRANS LOADELIM cases                                                | 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Compile-time overheads for functions with the largest interference      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| graphs in SPECint2000 benchmarks                                        | 177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                         | Comparison of SC and JMM for compile reordering transformation .  Comparison of compile-time and profile-driven bitwidth analysis  Comparison of Active Compression Factor (ACF) across static and profile-driven bitwidth analysis  New EMIW estimates for variable packing using NODEMAX  Static count of parallel constructs in various benchmarks  Compilation time in milliseconds of various benchmarks for NO LOADELIM, FKS LOADELIM, and FKS+TRANS LOADELIM cases. Compilation times in milliseconds of various benchmarks for PAR LOADELIM and PAR+TRANS LOADELIM cases  Dynamic counts of GETFIELD operations using FKS LOADELIM and FKS+TRANS LOADELIM cases |

| 8.7  | Benchmarks for which register-to-register move and register exchange |     |

|------|----------------------------------------------------------------------|-----|

|      | instructions were generated                                          | 180 |

| 8.8  | Compile-time comparison of $ELS$ with $LS$ in Jikes RVM              | 182 |

| 8.9  | Comparison of number of packed node-pairs for the number of          |     |

|      | physical registers=8                                                 | 184 |

| 8.10 | Comparison of dynamic spill load/store instructions                  | 185 |

# Chapter 1

# Introduction

The computer industry is at a major inflection point in its hardware roadmap due to the end of a decades-long trend of exponentially increasing clock frequencies. Unlike previous generations of hardware evolution, the shift towards multicore and manycore computing will have a profound impact on software — not only will future applications need to be deployed with sufficient parallelism for manycore processors, but the parallelism must also be energy-efficient. For decades, caches have helped bridge the memory wall for programs with high spatial and temporal locality. Unfortunately, caches come with an energy cost that limits their use as on-chip memory in future manycore processors. It is therefore desirable for programs to use more energy-efficient storage structures such as registers and local memories (scratchpads) instead of caches, as far as possible.

Energy-efficient storage structures offer lower latencies and are faster to access. However, they are smaller in size and number due to architectural complications involved in their design. For example, the Intel x86 architecture offers only 8 fixed registers for integer valued data items. A compiler that converts a higher-level program into an optimized machine level instruction sequence performs several optimizations in order to improve the execution performance of a program. One such optimization that focuses on improving memory accesses in the program is memory-access optimization. The goal of a memory-access optimization is to promote frequently executed data values from memory (with higher latency of access) to more efficient structures like registers and local memories in order to take advantage of their lower latencies and faster accesses. Several compiler optimizations have been proposed in the literature

that address optimization for memory accesses such as scalar replacement [33, 34], load elimination [52, 75, 102], redundant memory operation analysis [45], and register promotion [83]. The compiler community has studied these techniques extensively over three decades and have shown benefits of performing them inside a compiler.

Gordon Moore predicted in 1965 that the number of transistors on a machine would double every eighteen months. This trend has been observed for a long period of time. In the past, this increase in the number of transistors (and decrease in transistor sizes) has led to a corresponding increase in clock frequency. However, recently, the power wall has caused a trend shift from serial to parallel computing by introducing more and more low power cores in a processor. All hardware vendors now ship systems with multi-core processors. The performance gain by the introduction of multi-core processors is strongly dependent on the software algorithms and their implementation. For example, in order to achieve speedup on a quad-core machine, it is necessary to exploit the four cores in software. Hence, new programming languages like MPI [109], UPC [51], OpenMP [95], Cilk [18], X10 [38], and Titanium [63] have been developed to expose the available parallelism on a multi-core processor to the application programmer. Along with new programming languages for parallelism, there is a need for new compiler techniques to analyze the parallel constructs of the language and optimize programs keeping parallelism in mind. Currently, most compilers make conservative assumptions for parallel constructs and hence, miss several opportunities for code optimization including memory-access optimization. For example, the Jikes RVM [66] prevents code motion around parallel constructs.

Parallelism poses another challenge to compiler transformations in the form of *interferences* among shared data accesses of multiple cores. The legality of a compiler transformation in the presence of interferences is typically dictated by the underlying memory model. A memory model determines the set of possible observable behaviors of the program. A compiler transformation is said to be correct if the set of possible observable behaviors of the transformed program is a subset of the possible observable

behaviors of the original programs. All memory models have the same semantics for a data-race-free program. However, without prior knowledge, a compile does not know if the input program is data-race free or not. Hence, it is desirable to define a memory model for parallel programs that is both programmer and compiler friendly and at the same time allows for more opportunities for compiler optimizations, which is critical for program performance. Note that memory-access compiler optimizations are often viewed as a variant of code reordering transformations, because they can result in a reordering of load and store instructions, and hence, are correct to perform under a given memory model.

In conjunction with the hardware trend shift from serial computing to parallel computing, in dynamic compilation, program execution and compilation can be interleaved. Dynamic compilation is also referred to as Just-In-Time (JIT) compilation and runtime compilation. For example, the platform-independent bytecodes of a Java program are usually compiled and executed by a virtual machine that invokes a JIT compiler. A dynamic compiler shares the *common* goal of producing optimized code with that of an offline/static compiler. However, a key difference is that in a dynamic compiler the compilation time overhead adds to the runtime performance. The optimizations performed in a dynamic compiler must strike a balance between performing deeper analysis (with higher complexity) and runtime benefits achieved from them. In practice, the optimizations must be performed as close to linear time and space as possible. For example, the Linear Scan register allocation algorithm proposed by Poletto and Sarkar [100] is performed by many Java virtual machine JIT compilers due to its linear time and space complexity instead of the Graph Coloring register allocation approach [25, 28, 35] used in static compilation. However, Linear Scan is known to lag in runtime performance compared to Graph Coloring approaches.

Thesis Statement: Recent trends in hardware with multi-core processors as well as software with parallel languages and dynamic compilation have added new challenges to the Memory Wall problem. Our thesis is that a combination of high-level

and low-level compiler optimizations can be effective in addressing these challenges. The high-level optimizations introduced in this thesis include new approaches to May-Happen-in-Parallel analysis, Side-Effect analysis, and Scalar Replacement for Load Elimination transformation for explicitly parallel programs. The low-level dynamic optimizations include a Space-efficient register allocation algorithm that incurs an order-of-magnitude smaller compile-time and space overhead than Graph Coloring, while delivering run-time performance that matches or surpasses that of Graph Coloring.

#### 1.1 Research Contributions

This dissertation highlights the challenges in memory-access optimization for parallel programs, using X10 as an example parallel programming language. The X10 v1.5 language [38] builds on a subset of Java language constructs and adds new constructs like async, finish, atomic, places, region, distribution, and distributed arrays for supporting fine-grained locality, parallelism and synchronization. Since, version 1.7, X10 has adopted a Scala-like syntax for source code and has introduced new advances in the type system relative to Java. The Habanero-Java (HJ) programming language that is being developed in the Habanero Multicore Software Research project at Rice University focuses on addressing the implementation challenges for the core constructs of X10 v1.5 language on multi-core processors, with programming model extensions as needed (such as phasers and isolated blocks). A significant part of the research results presented in this thesis were obtained for HJ programs.

The dissertation makes the following contributions:

1. a novel May-Happen-in-Parallel (MHP) algorithm for HJ programs that identifies pairs of execution instances of statements that may execute in parallel. Compared to past work for other concurrent languages like Java and Ada, we introduce a more precise definition of the MHP by adding condition vectors that distinguishes execution instances of statements for which the MHP holds,

instead of just returning a single true/false value for all pairs of executing instances. The availability of basic concurrency control constructs such as async, finish, isolated and places in HJ enables the use of more efficient and precise analysis algorithms based on simple path traversals in a Program Structure Tree.

- 2. a *side-effect* analysis for the core parallel constructs of HJ. The side-effect analysis is designed for dynamically compiling HJ programs and hence, is compiletime efficient.

- 3. a novel parallelism-aware scalar replacement transformation for memory load elimination. The legality of the transformation is established by a new Isolation Consistency (IC) memory model. Like many relaxed memory models, the IC memory model provides sequentially consistent behavior for data-race-free programs. At the same time, IC allows many compiler transformations via weak-atomicity for programs with data-races.

- 4. a space-efficient register allocation algorithm that bridges the performance gap between Linear Scan and Graph Coloring register allocation algorithms while maintaining the compile-time efficiency of Linear Scan. We model the allocation phase of a register allocation algorithm as an optimization problem on Bipartite Liveness Graphs (BLG's), a new data structure introduced in this thesis. The assignment phase focuses on reducing the number of spill instructions by using register-to-register move and exchange instructions wherever possible to maximize the use of registers. The register assignment that includes register-to-register moves, exchanges, coalescing as well as register class constraints is modeled as another optimization problem, and we provide a heuristic solution to this problem as well.

- 5. an enhanced bitwidth-aware register allocation algorithm that packs several narrowwidth data items onto the same physical register to reduce register pressure of

the program. We present an *enhanced bitwidth analysis* that performs more detailed scalar analysis and array analysis than past work. We describe an *enhanced packing* algorithm that includes *more accurate* packing and performs less conservative (more aggressive) coalescing than past work.

## 1.2 Thesis Organization

- Chapter 2 introduces necessary backgrounds, definitions and notations used in the thesis. The overall code optimization framework used in the thesis is also described in this chapter.

- Chapter 3 describes the May-Happens-in-Parallel algorithm for HJ programs.

- Chapter 4 presents the Side-Effect Analysis for parallel constructs and function calls.

- Chapter 5 describes the Isolation Consistency (IC) memory model and scalar replacement for load elimination transformation for parallel programs.

- Chapter 6 describes the space-efficient register allocation algorithm and compares it with the graph coloring register allocation.

- Chapter 7 presents our enhancements to bitwidth-aware register allocation algorithm.

- Chapter 8 presents our experimental results.

- Chapter 9 concludes the thesis with a summary and future directions.

# Chapter 2

# Background

In this chapter, we introduce notations and terminologies used in the rest of the dissertation. First, we describe some basic compiler terminologies. Next, we describe the HJ parallel programming language. Next, we present our overall code optimization framework for parallel programs. Finally, we describe the background, foundations and notations for each of the analyses and optimizations described in our code optimization framework.

### 2.1 Basics of a Compiler

A compiler (static or dynamic) typically consists of two components: a front-end and a back-end. In the front-end, the input program is parsed, represented as an intermediate representation (IR), and transformed. Typical transformations performed in the front-end are deadcode elimination, constant propagation, copy propagation, and inlining. After the front-end pass is complete, the back-end component performs additional transformations that are specific to the target architecture. Typical transformations performed in the back-end are register allocation, instruction scheduling, and instruction selection. Sometimes compilers add a middle-end that consists of the transformations of the front-end.

An *IR* captures the compiler's knowledge of the input program. It consists of a set of *instructions* that correspond to the original input program.

**Definition 2.1.1** An instruction defines an operation that possibly reads some variables and possibly writes some other variables. The variables that are read at an

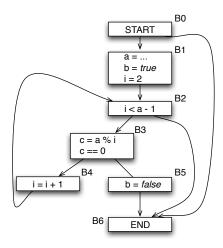

Figure 2.1: An example control flow graph. The code snippet is shown on the left. The corresponding control flow graph is shown in the right. Note that, the special basic blocks START and END are added to demarcate entry and exit to the procedure.

instruction are referred to as used variables and those that are written are referred to as defined variables.

An IR can be represented in various ways. Some dominant IR representations are: 1) a linear IR consisting of a linear ordering of instructions, e.g., Java bytecode; 2) a structural IR consisting of graphical representations of instructions, e.g., abstract syntax trees; 3) linear+structural IR consisting of a combination of graphical representation and linear ordering, e.g., control flow graph (CFG). A CFG-based representation is widely used for compiler analyses and transformations.

**Definition 2.1.2** A control flow graph is a graph,  $G = \langle V, E \rangle$ , where V consists of basic blocks and E consists of possible execution paths. A basic block is a maximal sequence of instructions where the execution enters at the first instruction and exits at the last instruction of the sequence, i.e., there exists no intermediate instruction in a basic block where an execution can enter or exit. Two special basic blocks START and END are added to a CFG to indicate the unique entry and unique exit of a procedure.

Consider the example program shown in Figure 2.1. The example program computes if a is a prime number or not. The control flow graph (CFG) is shown on the right. It consists of seven basic blocks, *i.e.*, B0-6, including two special entry and exit basic blocks B0 and B6, respectively. The basic block B3 consists of two instructions c = a%i and c = 0. For instruction c = a%i, variables a and b are b whereas b is b defined.

Often it is useful to define dom, idom, and postdom relationships between two nodes of a CFG.

**Definition 2.1.3** Given a CFG, a node x is said to dominate (dom) another node y if every path from START to y passes through x. Similarly, node x is said to post-dominate (postdom) node y if every path from y to EXIT passes through x. A node x is the immediate dominator (idom) of another node y if x dominates y and there is no intervening node p such that x dom p and p dom y. The idom relation forms a dominator tree.

For precision, it is often necessary to represent information in between two instructions. For example, the *liveness* of a variable needs to be defined at a *program* point rather than at an instruction level.

**Definition 2.1.4** A program point is a point between two consecutive instructions.

**Definition 2.1.5** A variable v is live at a program point p if  $\exists$  a path in the CFG (indicating a possible execution) from p to some use of v along which v is not defined again. As we will discuss in Definition 2.7.5, sometimes it is desired to split a program point into two sub-program points.

A popular intermediate representation used in the literature is static single assignment (SSA) form [47]. In SSA form representation, each variable is defined in exactly one place in the code. New  $\phi$  instructions are inserted in the CFG to ensure that each use of a variable sees exactly one definition. An IR is converted into SSA form using two simple steps: (1)  $\phi$ -insertion phase:  $\phi$  statements are inserted at the iterated dominance frontiers of assignment statements [48]; (2) renaming phase: the renaming phase assigns unique names using version ids to each variable definition. Several efficient transformations have been proposed in literature that exploit the single-assignment property of SSA form such as sparse-conditional constant propagation [122], strength reduction [46], partial redundancy elimination [41] and SSA based register allocation [29, 59]. We will describe SSA based register allocation in Section 2.7.2.3.

A common compiler transformation is to find redundant expressions in a program. An expression a + b is said to be redundant at a program point p if it has already been computed in every path starting from the START block to p, and no intervening operation kills either a or b. If the compiler can find such redundant expressions, it can save the value in a scalar variable at the previous computation and replace any subsequent computations with the scalar variable. The classic approach to accomplish this is to use  $Value\ Numbering\ [6]$ . Value numbering assigns distinct numbers to each value computed during run time. Two expressions,  $e_1$  and  $e_2$ , have same  $value\ number$  iff they always compute the same value. We denote the value number of an expression e as  $\mathcal{V}(e)$ . If the value numbers of two expressions are same, then they are redundant.

An ordering-based compiler transformation such as redundant expression elimination is said to be correct if it does not violate any *dependences*. A *control dependence* arises from the control flow in the program, where as a *data dependence* arises from the flow of values between statements in the program.

#### **Definition 2.1.6** The following types of data dependences exist:

- 1. Statements  $S_1$  and  $S_2$  are said to have a flow dependence between them (denoted as  $S_1\delta_f S_2$ ) if  $S_2$  uses the value written at  $S_1$ .

- 2. Statements  $S_1$  and  $S_2$  are said to have an anti-dependence between them (denoted as  $S_1\delta^{-1}S_2$ ) if  $S_1$  uses a value from a location to which  $S_2$  writes.

- 3. Statements  $S_1$  and  $S_2$  are said to have an output dependence between them (denoted as  $S_1\delta^oS_2$ ) if both  $S_1$  and  $S_2$  write to the same location.

- 4. Statements  $S_1$  and  $S_2$  are said to have an input dependence between them (denoted as  $S_1\delta^iS_2$ ) if both  $S_1$  and  $S_2$  use a value from the same location.

A succinct way of capturing dependences for statements inside a loop is to use distance and direction vectors.

**Definition 2.1.7** Given a dependence from statement  $S_1$  on iteration i to statement  $S_2$  on iteration j of a common loop nest l, the direction vector  $\mathcal{D}(i,j)$  is defined as a vector of length l such that,

$$\mathcal{D}(i,j)_{k} = \begin{cases} < & if \ j_{k} - i_{k} > 0 \\ = & if \ j_{k} - i_{k} = 0 \\ > & if \ j_{k} - i_{k} < 0 \end{cases}$$

(2.1)

Various dependences between the statements in a program are represented using a program dependence graph (PDG). PDG's are used as the foundation for many compiler reordering transformations such as vectorization, scalar replacement, and scheduling.

# 2.2 The HJ Parallel Programming Language

The HJ programming language offers several constructs to improve programmability in high-performance computing for parallel systems that includes multi-core processors, symmetric shared-memory multiprocessors (SMPs), commodity clusters, highend supercomputers like BlueGene [1], and even embedded processors like Cell [99]. The key features of HJ include:

• Lightweight *activities* embodied in async, future, foreach, and ateach constructs which subsume communication and multithreading operations.

- A finish construct for termination detection and rooted exception handling of descendant activities.

- Support for lock-free synchronization with isolated blocks.

- Explicit reification of locality in the form of places, with support for a partitioned global address space (PGAS) across places.

- Support for collective and point-to-point communication using phaser constructs.

HJ uses a serial subset of the Java v1.4 language as its foundation, but replaces the Java language's current support for concurrency by new constructs that are motivated by high-productivity high-performance parallel programming. For further details, the reader is referred to "An overview of X10 v1.5" [38]. The scope of this dissertation focuses on four core constructs: async, finish, isolated, and places. Extensions for the foreach, ateach, and future constructs follow naturally from the approach described in this thesis, and have been omitted for simplicity. An important safety result in HJ is that any program written with async, finish, and isolated can never deadlock.

#### 2.2.1 Single Place HJ Language Constructs

In a single-place HJ program, all activities execute within the same logical *place* and have uniform read and write access to all shared data, as in multithreaded Java programs where all threads operate on a single shared heap.

**async**  $\langle \mathbf{stmt} \rangle$ : Async is the HJ construct for creating or forking a new asynchronous activity. The statement,  $async \langle stmt \rangle$ , causes the parent activity to create a new child activity to execute  $\langle stmt \rangle$ . Execution of the async statement returns immediately *i.e.*, the parent activity can proceed immediately to the statement following the async.

Consider the following HJ code example of an async construct. The goal of this example is to use two activities to compute in parallel the sums of f(i) for odd and even values of i in the range  $1 \dots n$ . This is accomplished by having the main program activity use the *async for-i* statement to create a child activity to execute the *for-i* loop and print *oddSum*, while the parent (main program) activity proceeds in parallel to execute the *for-j* loop and print *evenSum*<sup>1</sup>.

```

public static void main(String[] args) {

final int n = 10000;

async { // Compute oddSum in child activity

double oddSum = 0;

for (int i=1 ; i<=n ; i+=2) oddSum += f(i);

System.out.println("oddSum = " + oddSum);

}

// Compute evenSum in parent activity

double evenSum = 0;

for (int j=2 ; j<=n ; j+=2) evenSum += f(j);

System.out.println("evenSum = " + evenSum);

} // main()</pre>

```

$\mathsf{HJ}$  permits the use of async to create multiple nested activities in-line in a single method, unlike  $\mathsf{Java}$  threads where the body of the thread must be specified out-of-line in a separate  $\mathsf{Runnable}$  class. Also, note that the child activity uses the value of local variable n from the parent activity, without the programmer having to pass it explicitly as a parameter.  $\mathsf{HJ}$  provides this sharing of local variables for convenience, but requires that any local variables in the parent activity that are accessed by a child activity must be defined as final (constant) in the parent activity so as to ensure that no data races can occur on local variables.

finish  $\langle \mathbf{stmt} \rangle$ : The HJ statement,  $finish \langle stmt \rangle$ , causes the parent activity to execute  $\langle stmt \rangle$  and then wait till all sub-activities created within  $\langle stmt \rangle$  have terminated

<sup>&</sup>lt;sup>1</sup>Function f is assumed to be a pure function of its input i, and to involve sufficient computation granularity to ensure that the async overhead is insignificant in these examples.

globally. There is an implicit *finish* statement surrounding the main program in an HJ application. If async is viewed as a fork construct, then finish can be viewed as a join construct. However, the async-finish model is more general than the fork-join model [38].

HJ distinguishes between *local termination* and *global termination* of a statement. The execution of a statement by an activity is said to terminate locally when the activity has completed all the computation related to that statement. For example, the creation of an asynchronous activity terminates locally when the activity has been created. A statement is said to terminate globally when it has terminated locally and all activities that it may have spawned (if any) have, recursively, terminated globally.

Consider a variant of the previous example in which the main program waits for its child activity to finish so that it can print the total sum obtained by adding *oddSum* and *evenSum*:

The finish statement guarantees that the child activity terminates before the print statement is executed. Note that the result of the child activity is communicated to the parent in a shared object, *oddSum*, since HJ does not permit a child activity to update a local variable in its parent activity.

In addition to waiting for global termination, the finish statement plays an important role with regard to exception semantics. An HJ activity may terminate normally or abruptly. A statement terminates abruptly when it throws an exception that is not handled within its scope; otherwise it terminates normally. While it may seem that an obvious solution is to propagate exceptions from a child activity to a parent activity, doing so is problematic when the parent activity terminates prior to the child activity. Since we want to permit child activities to outlive parent activities in HJ, the finish construct is a more natural collection point for exceptions thrown by descendant activities. HJ requires that if statement S or an activity spawned by S terminates abruptly, and all activities spawned by S terminate, then finish S terminates abruptly and throws a single exception formed from the collection of all exceptions thrown by S or its descendant activities. Exceptions thrown by this statement are caught by the runtime system and result in an error message printed on the console. This provides more robust exception handling support for multithreaded programs compared to the Java model in which an exception is simply propagated from a thread to the top-level console instead of propagation to an appropriate handler in an ancestor thread.

isolated  $\langle stmt \rangle$ , isolated  $\langle method\text{-}decl \rangle$ : An isolated block is executed by an activity as if in a single step during which all other concurrent activities within the same place are suspended. The isolated construct is our renaming of X10's atomic construct. As stated in [38], an atomic block in X10 is intended to be "executed by an activity as if in a single step during which all other concurrent activities in the same place are suspended". This definition implies a strong atomicity semantics for the atomic construct. However, all X10 implementations that we are aware of (including the one used in this paper) use a single lock per place to enforce mutual exclusion of atomic blocks. This approach supports weak atomicity, since no mutual exclusion guarantees are enforced between computations within and outside an atomic block.

As advocated in [73], we use the *isolated* keyword instead of *atomic* to make explicit the fact that the construct supports weak isolation rather than strong atomicity. An isolated block may include method calls, conditionals, and other forms of sequential control flow. Parallel constructs such as async and finish are not permitted in an isolated block. Isolated blocks may be nested and the isolated modifier on method definitions are permitted as a shorthand for enclosing the body of the method in an isolated block. The isolated construct is semantically equivalent to X10's *atomic* construct.

Consider the following example in which each iteration of a loop executes in parallel and accumulates its result in a shared location, *Sum.val*:

```

public static void main(String[] args) {

final int n = 10000;

final BoxedDouble Sum = new BoxedDouble();

finish

for (int i = 1 ; i <= n ; i++ )

async { // Compute oddSum in child activity

double result = f(i);

isolated Sum.val += result;

}

System.out.println("Sum = " + Sum.val);

} // main()</pre>

```

In the previous example, the finish construct was used to ensure that shared location oddSum.val was computed by the child activity before it was read by the parent activity. In this example, the shared location Sum.val can be updated in parallel by multiple activities, and the isolated block is used to ensure that the read-modify-write operations are performed in a consistent manner.

#### 2.2.2 Multi-Place Programming in HJ

Current programming models use two separate levels of abstraction for shared-memory thread-level parallelism (e.g., Java threads, OpenMP, pthreads) and distributed-memory

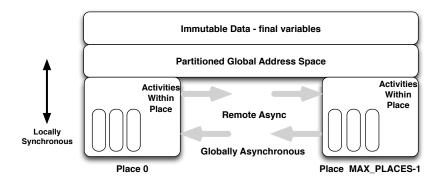

Figure 2.2: HJ's Multi-Place Execution Model

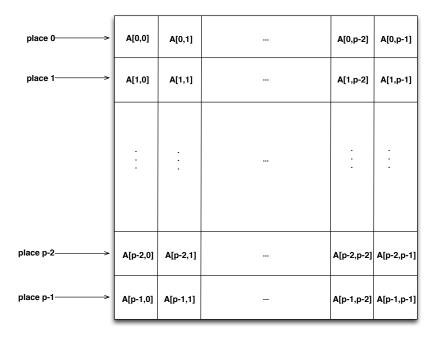

communication (e.g., Java messaging, RMI, MPI, UPC) resulting in significant complexity when trying to combine the two. The three core HJ constructs introduced earlier can be extended to multiple places, as illustrated in Figure 2.2. A place is a collection of resident (non-migrating) mutable data objects and the activities that operate on the data. Every HJ activity runs in a place; the activity may obtain a reference to this place by evaluating the constant *here*.

HJ takes the conservative decision that the number of places (MAX\_PLACES) is fixed at the time an HJ program is launched. Thus, there is no construct to create new places. This is consistent with current programming models, such as MPI, UPC, and OpenMP, that require the number of processes to be specified when an application is launched.

Places are virtual — the mapping of places to physical locations is performed by a deployment step that is separate from the HJ program [37, 125]. Though objects and activities do not migrate across places in an HJ program, an HJ deployment is free to migrate places across physical locations based on affinity and load balance considerations. While an activity executes at the same place throughout its lifetime, it may dynamically spawn activities in remote places.

HJ supports a partitioned global address space (PGAS) that is partitioned across places. Each mutable location and each activity is associated with exactly one place,

and places do not overlap. A scalar object in HJ is allocated completely at a single place. In contrast, the elements of an array, may be distributed across multiple places. We now discuss how the async and finish constructs discussed earlier in a single-place context, extend directly to the multi-place case.

#### 2.2.2.1 Remote Asyncs

The statement, **async** ( $\langle \text{place-expr} \rangle$ )  $\langle \text{stmt} \rangle$ , causes the parent activity to create a new child activity to execute  $\langle stmt \rangle$  at the place designated by  $\langle place-expr \rangle$ . The async is local if the destination place is same as the place where the parent is executing, and remote if the destination is different. Local async's are like lightweight threads, as discussed earlier in the single-place scenario. A remote async can be viewed as an *active message*, since it involves communication of input values as well as remote execution of the computation specified by  $\langle stmt \rangle$ . The semantics of the HJ finish operator is identical for local and remote async's viz., to ensure global termination of all asyncs created in the scope of the finish.

HJ supports a Globally Asynchronous Locally Synchronous (GALS) semantics for reads/writes to mutable locations. We say that a mutable variable is local for an activity if it is located in the same place as the activity; otherwise it is remote. An activity may read/write only local variables (this is called the *Locality Rule*, and it may do so synchronously. Any attempt by an activity to read/write a remote mutable variable results in a *BadPlaceException*. As mentioned earlier, isolated blocks are used to ensure atomicity of groups of read/write operations among multiple activities located in the same place. However, an activity may read/write remote variables only by spawning activities at their place. Thus a place serves as a coherence boundary in which all writes to the same datum are observed in the same order by all activities in the same place. In contrast, inter-place data accesses to remote variables have weak ordering semantics. The programmer may explicitly enforce stronger guarantees by using sequencing constructs such as finish.

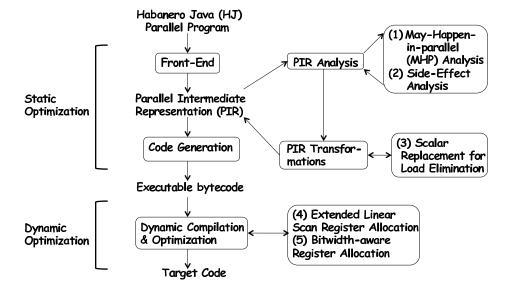

Figure 2.3: Static and Dynamic Optimization Framework

### 2.3 Code Optimization Framework

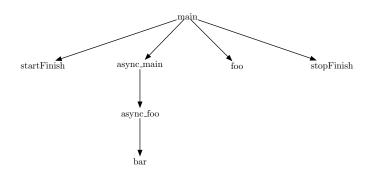

Figure 2.3 depicts the overall compiler analysis and optimization framework assumed in this thesis. The overall compiler infrastructure consists of a static optimization component and a dynamic optimization component. The input parallel programming language considered is HJ, however the techniques described in this thesis can be applied to other parallel programming languages as well. The input parallel program is parsed by the *front-end* of the static optimizer and is translated into a *parallel intermediate representation* (*PIR*). *PIR* is an intermediate representation in which the parallel constructs such as async, and finish are explicitly represented in a hierarchical manner. Like other intermediate representations, several analyses and transformations are performed at the *PIR* level.

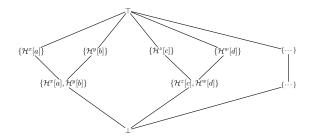

One of the key foundations of analyzing parallel programs is to determine statement instances that may execute in parallel with each other. This is known as May-Happen-in-Parallel (MHP) analysis. The MHP information can be used in other compiler analysis and optimization of parallel programs e.g., the constant

propagation described in [77] using concurrent-SSA form representation needs to know the interfering data values and these can be determined using the MHP analysis. In this thesis, we present a precise definition of MHP using condition vectors that identify execution instances of statements for which the MHP holds, instead of just returning a single true/false value for all pairs of executing statement instances. Based on this definition, we present an efficient algorithm for computing MHP information for HJ parallel programs. Compared to the MHP analysis of other languages, our approach [2] is based on a simple walk over the program structure tree which is an abstraction of the abstract syntax tree. The MHP analysis analyzes async, finish, isolated, and places constructs of HJ.

Traditionally, procedure calls hinder the precision of compiler transformations in the absence of interprocedural analysis. Side-effect analysis is an interprocedural analysis that summarizes the modified and referenced data items for each procedure. For parallel programs, the parallel constructs themselves embed inherent side-effects. To enable PIR transformations across procedure boundaries and parallel constructs, we present a unified side-effect analysis in this thesis that summarizes side-effects of procedure calls in the presence of parallel constructs. The side-effect analysis [12] uses a heap-array representation for faster side-effect computation. It computes side-effects for unique features of HJ programs like global termination using finish and escaping-async. The side-effects can be used by other code reordering transformations such as code motion.

After PIR analysis is performed, several PIR transformations are performed. One such PIR transformation is scalar replacement for load elimination that replaces memory load operations of object references by scalar variables, thereby enabling the back-end to generate register accesses instead of load instructions. In this thesis, we describe a parallelism-aware scalar replacement transformation for eliminating memory load operations. The legality of such a transformation in parallel programs is strongly dependent on the underlying memory model supported by the programming

language. We describe an Isolation Consistency (IC) memory model [12] for HJ parallel programs. IC is a weak memory model that allows more opportunities for code reordering than other existing weaker memory models described in past work [21, 53, 64, 84]. After transformations are applied at the *PIR* level, platform-independent bytecode is produced for the input HJ parallel program.