1-Gigabit Ethernet MAC Core with PCS/PMA Sublayers (1000BASE-X) or GMII v4.0

**Product Specification**

DS200 December 11, 2003

## **Features**

Single-speed 1-gigabit/second Ethernet Media Access Controller (MAC)

- Designed to IEEE 802.3-2002 specification

- Reconciliation sublayer with optional GMII

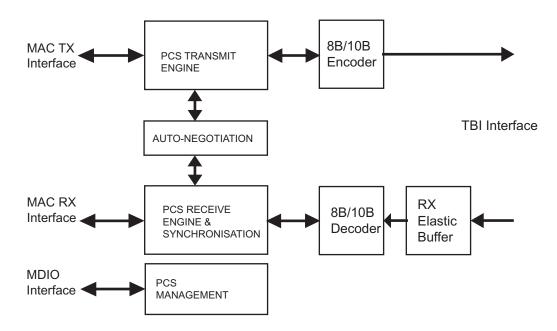

- Optional Full-Duplex Physical Coding Sublayer (PCS) for 1000BASE-X with Ten-Bit Interface (TBI) in the Virtex-II and Spartan-3 families

- Optional Full-Duplex Physical Coding Sublayer (PCS) with Physical Medium Attachment (PMA) for 1000BASE-X in the Virtex-II Pro family

- Configurable Half Duplex and Full Duplex operation with GMII in the Virtex-II family

- Configured and monitored through an independent microprocessor-neutral interface

- Powerful statistics gathering to internal counters (statistic vectors are also output externally for user access)

- Configurable flow control through MAC Control pause frames; symmetrically or asymmetrically enabled

- Optional MDIO interface to managed objects in PHY layers (MII Management)

- Support of VLAN frames to specification IEEE 802.3-2002

- Configurable support of jumbo frames of any length

- · Configurable inter frame gap adjustment

- Configurable in-band FCS field passing on both transmit and receive paths

- Optional PCS supports Auto-Negotiation for information exchange with a link partner

- Available under terms of the SignOnce IP License

| LogiCORE™ Facts           |                                   |  |  |  |

|---------------------------|-----------------------------------|--|--|--|

| Core S                    | pecifics                          |  |  |  |

|                           | Virtex™-E (-7)                    |  |  |  |

| Supported Family          | Virtex-II™ (-4)                   |  |  |  |

| (GMII configuration)      | Virtex-II Pro™(-5)                |  |  |  |

| (Own comiguration)        | Spartan™-IIE (-7)                 |  |  |  |

|                           | Spartan-3 (-4)                    |  |  |  |

| Supported Family          | Virtex-II (-4)                    |  |  |  |

| (1000BASE-X PCS with      | Virtex-II Pro(-5)                 |  |  |  |

| TBI configuration)        | Spartan-3 (-4)                    |  |  |  |

| Supported Family          |                                   |  |  |  |

| (1000BASE-X PCS & PMA     | Virtex-II Pro(-5)                 |  |  |  |

| configuration)            |                                   |  |  |  |

| Performance               | 125 MHz internal clock;           |  |  |  |

| Size                      | 581 - 1850 slices                 |  |  |  |

| Global Clock Buffers      | 2 - 4                             |  |  |  |

| Provided                  | with Core                         |  |  |  |

| Documentation             | Product Specification             |  |  |  |

| Design File Formats       | EDIF and NGC netlist, HDL wrapper |  |  |  |

| Constraints File          | UCF                               |  |  |  |

| Design Tools Requirements |                                   |  |  |  |

| Xilinx Core Tools         | v6.1i SP3                         |  |  |  |

| Sup                       | Support                           |  |  |  |

| Provided by Xilinx        |                                   |  |  |  |

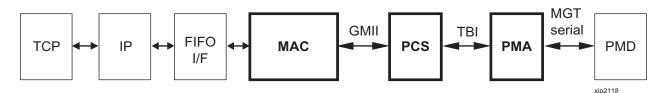

Figure 1: Typical Gigabit Ethernet Architecture

© 2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

#### **MAC Overview**

The 1-Gigabit Ethernet MAC is part of the Ethernet architecture displayed in Figure 1. The part of this architecture from the MAC to the right is defined in specification IEEE 802.3-2002.

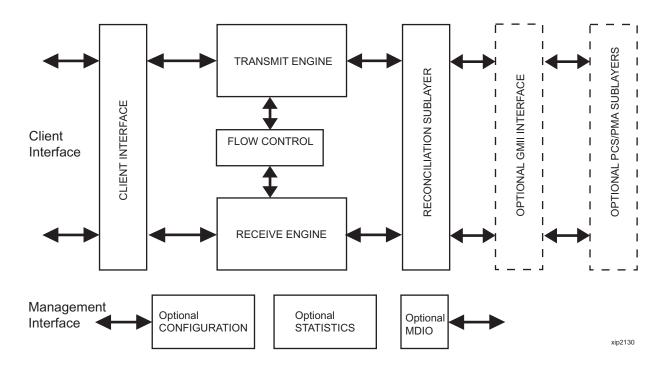

A block diagram of the MAC core is displayed in Figure 2, which shows the major functional blocks of the MAC:

- Client interface

- Transmit engine

- Flow control block

- Receive engine

- Reconciliation sublayer (RS)

- · Optional management interface and MDIO

- Optional statistics block

- Optional GMII interface

- Optional PCS/PMA sublayers for 1000BASE-X

The client interface has fully independent 8-bit interfaces for both transmit and receive to support full-duplex operation.

Configuration of the core, access to the statistics block and access to the MDIO port are accessed through the optional management interface, a 32 bit processor-neutral data pathway that is independent of the Ethernet data pathway. When the management interface is omitted, configuration of the core can still be made via an alternative configuration vector.

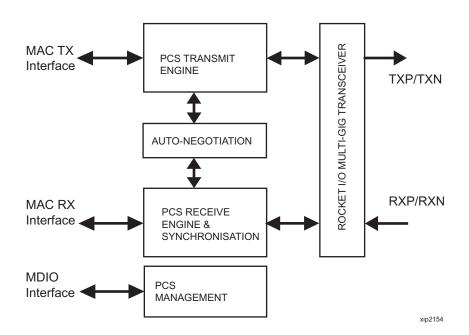

The Gigabit Media Independent Interface (GMII) is the interface available to all supported device families. In the Virtex-II family, the GMII can be replaced by a 1000BASE-X PCS with Ten Bit Interface (TBI). In the Virtex-II Pro family, the GMII or TBI can be replaced with 1000BASE-X PCS and PMA sublayers; this uses the Rocket I/O™ Multi-Gigabit Transceiver (MGT) technology to transmit and receive 1.25 Gbp/s serial data over differential lines

Figure 2: Functional Block Diagram of the 1 Gigabit Ethernet MAC

## Xilinx CORE Generator

The 1-Gigabit Ethernet MAC Core is generated through the Xilinx CORE Generator™ system. The following sections describe the graphical user interface (GUI) options and the generated output files.

#### **GUI Interface**

## Component Name

The component name is used as the base name of the output files generated for the core. Names must begin with a letter and must be composed from the following characters: a through z, 0 through 9 and "\_".

## Half Duplex Capable

Select this option to have the MAC work in both full-duplex and half-duplex modes, select the Half Duplex Capable option.

The default is half-duplex capability. Note that half-duplex capability is not supported in the Virtex-E or Spartan-IIE families.

## Management Interface

Select this option if you wish to include the optional Management Interface (see page 30). If this option is not selected, the core will be generated with a configuration vector.

The default is to have the management interface.

#### Statistics Gathering

Select this option to include the optional Statistical Gathering with the core (see page 34). This option is available only if the core includes the optional management interface. The statistics vectors are available whether or not this option is selected.

The default is to gather statistics.

# **Memory Type**

If the statistics gathering option is selected, it is possible to choose which memory type the statistics are stored in. The choices are *Block Memory* or *Distributed Memory*. The choice of these should be based on the availability of resources in your design. There is no performance or functional difference between the memory types.

The default type is the *Block Memory*. Note that *Distributed Memory* is not supported in the Virtex-E or Spartan-IIE families.

## Physical Interface

Depending on the target Xilinx FPGA architecture, it may be possible to select from three different physical interface choices for the core:

- GMII see the optional GMII on page 40

- TBI see the optional PCS on page 43

- PHY see the optional PCS & PMA sublayers on page 46

The *TBI* option is not supported in the Virtex-E or Spartan-IIE families. The *PHY* option is supported in the Virtex-II Pro family only.

The default is the GMII physical interface.

#### Parameter Values in the XCO File

XCO file parameter names and their values are identical to the names and values shown in the GUI, except that underscore characters (\_) are used instead of spaces. The text in an XCO file is case insensitive.

Table 1 shows the XCO file parameters and values, and summarizes the GUI defaults. The following is an example of the CSET parameters in an XCO file:

```

CSET component_name = abc123

CSET physical_interface = gmii

CSET statistics_gathering = true

CSET half_duplex_capable = true

CSET memory_type = block_memory

CSET management interface = true

```

Table 1: XCO File Values and Default Values

| Parameter            | XCO File Values                                                                            | Default GUI Setting |

|----------------------|--------------------------------------------------------------------------------------------|---------------------|

| component_name       | ASCII text starting with a letter and based upon the following character set: az, 09 and _ | blank               |

| physical_interface   | One of the following keywords: gmii, tbi, phy                                              | gmii                |

| statistics_gathering | One of the following keywords: true, false                                                 | true                |

| half_duplex_capable  | One of the following keywords: true, false                                                 | true                |

| memory_type          | One of the following keywords: block_memory, distributed_memory                            | block_memory        |

| management_interface | One of the following keywords: true, false                                                 | true                |

# **Output Generation**

The output files generated from the CORE Generator are placed in the CORE Generator project directory. The output files include: two netlist files, supporting CORE Generator files, a readme file and a subdirectory containing example wrapper files and scripts to take the core through the Xilinx implementation software and simulate the core using the

Modelsim simulator by Model Technology. See the generated readme files for explanations about these files.

## **Device Utilization**

Table 2 provides approximate slice counts for the core's various options when instantiated in a Virtex-II Pro device.

Table 2: Device Utilization

| Parameter Values |                  |     |                |                         |                       | D               | evice Resou | rces |           |      |      |

|------------------|------------------|-----|----------------|-------------------------|-----------------------|-----------------|-------------|------|-----------|------|------|

|                  | hysica<br>terfac |     |                | Statistics Gathering    |                       |                 |             |      |           |      |      |

| GMII             | тві              | PHY | Half<br>Duplex | Management<br>Interface | Distributed<br>Memory | Block<br>Memory | Slices      | LUT  | Registers | BRAM | GCLK |

| Yes              | No               | No  | Yes            | Yes                     | Yes                   | No              | 1545        | 2159 | 1654      | 0    | 3    |

| Yes              | No               | No  | Yes            | Yes                     | No                    | Yes             | 1420        | 1745 | 1561      | 2    | 3    |

| Yes              | No               | No  | Yes            | Yes                     | No                    | No              | 932         | 1140 | 991       | 0    | 3    |

| Yes              | No               | No  | Yes            | No                      | No                    | No              | 781         | 969  | 831       | 0    | 2    |

| Yes              | No               | No  | No             | Yes                     | Yes                   | No              | 1315        | 1752 | 1359      | 0    | 3    |

| Yes              | No               | No  | No             | Yes                     | No                    | Yes             | 1159        | 1525 | 1317      | 2    | 3    |

| Yes              | No               | No  | No             | Yes                     | No                    | No              | 742         | 884  | 793       | 0    | 3    |

| Yes              | No               | No  | No             | No                      | No                    | No              | 581         | 708  | 630       | 0    | 2    |

| No               | Yes              | No  | No             | Yes                     | Yes                   | No              | 1850        | 2345 | 1934      | 2    | 4    |

| No               | Yes              | No  | No             | Yes                     | No                    | Yes             | 1697        | 1880 | 1899      | 4    | 4    |

| No               | Yes              | No  | No             | Yes                     | No                    | No              | 1295        | 1404 | 1380      | 2    | 4    |

| No               | Yes              | No  | No             | No                      | No                    | No              | 1122        | 1226 | 1213      | 2    | 3    |

| No               | No               | Yes | No             | Yes                     | Yes                   | No              | 1725        | 1773 | 1791      | 0    | 3    |

| No               | No               | Yes | No             | Yes                     | No                    | Yes             | 1580        | 1838 | 1775      | 2    | 3    |

| No               | No               | Yes | No             | Yes                     | No                    | No              | 1172        | 1394 | 1236      | 0    | 3    |

| No               | No               | Yes | No             | No                      | No                    | No              | 1005        | 1183 | 1066      | 0    | 2    |

<sup>1.</sup> Half Duplex Logic is only available with the GMII.

<sup>2.</sup> Statistics Gathering is only available when the Management Interface is selected

# **Interface Description**

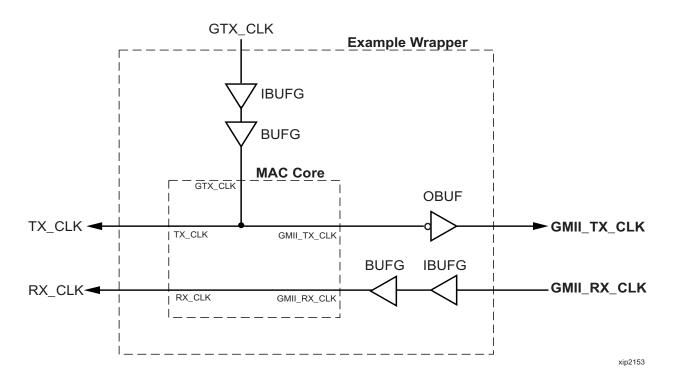

All ports of the core (with the exception of the Rocket I/O serial ports of the optional PCS/PMA sublayers) are internal connections in FPGA fabric. An example wrapper is delivered with the core which adds IBUFs, OBUFs and IOB flip-flops where appropriate to the external signals of the GMII or TBI. IOBs are also added to the remaining unconnected ports to allow the example design to be taken

through the Xilinx implementation software. In addition, all clock management logic is placed in this example wrapper; this allows the user more flexibility in implementation, for example, in designs using multiple cores.

The example wrapper is provided in both VHDL and Verilog.

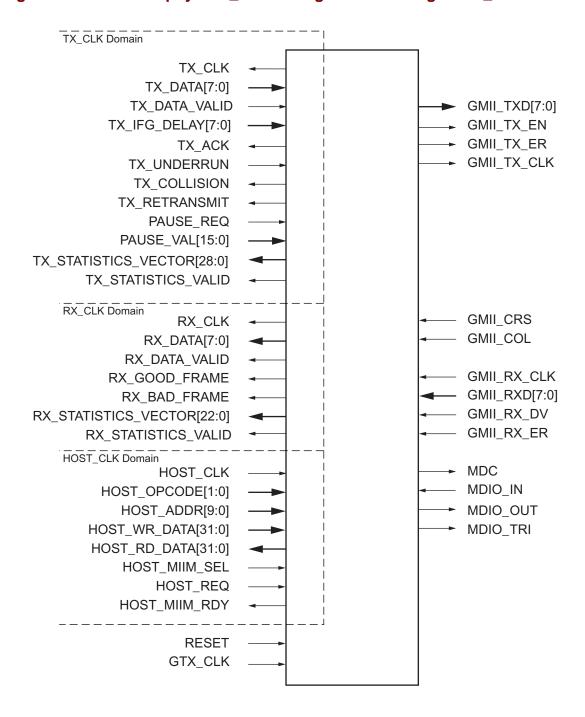

# Interface Signals for MAC with physical\_interface=gmii and management\_interface=true

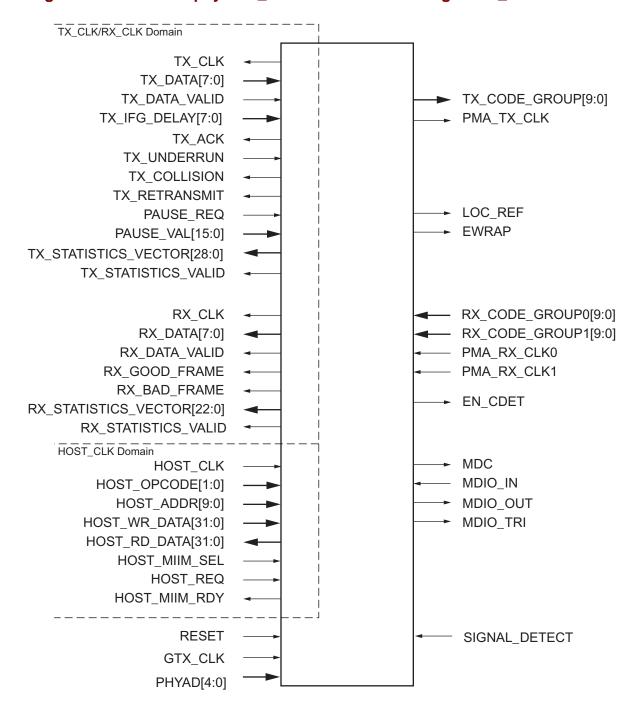

Figure 3: Component Pinout for MAC with GMII Interface using the optional Management Interface

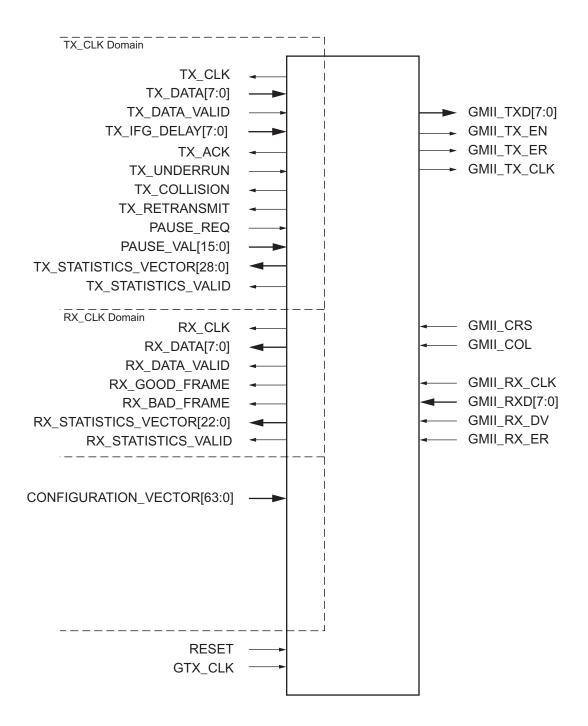

# Interface Signals for MAC with physical\_interface=gmii and management\_interface=false

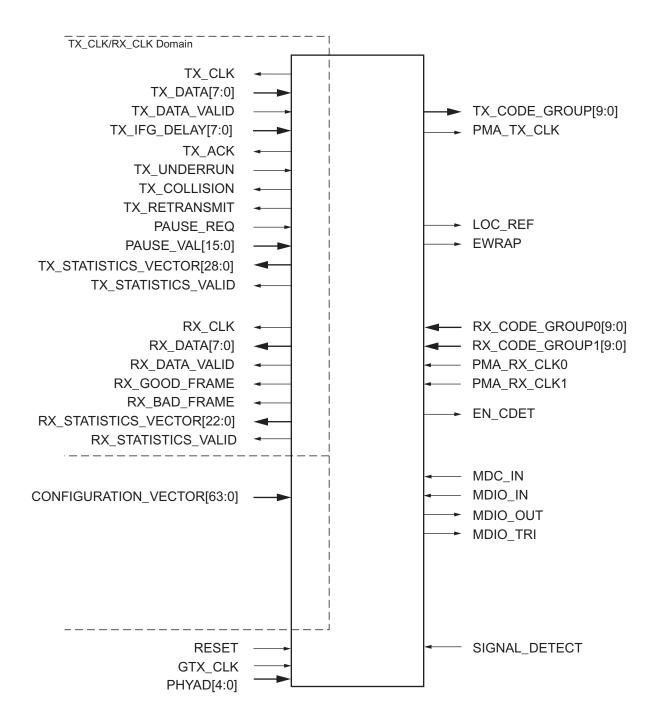

Figure 4: Component Pinout for MAC with GMII Interface without the optional Management Interface

## Interface Signals for MAC with physical\_interface=tbi and management\_interface=true

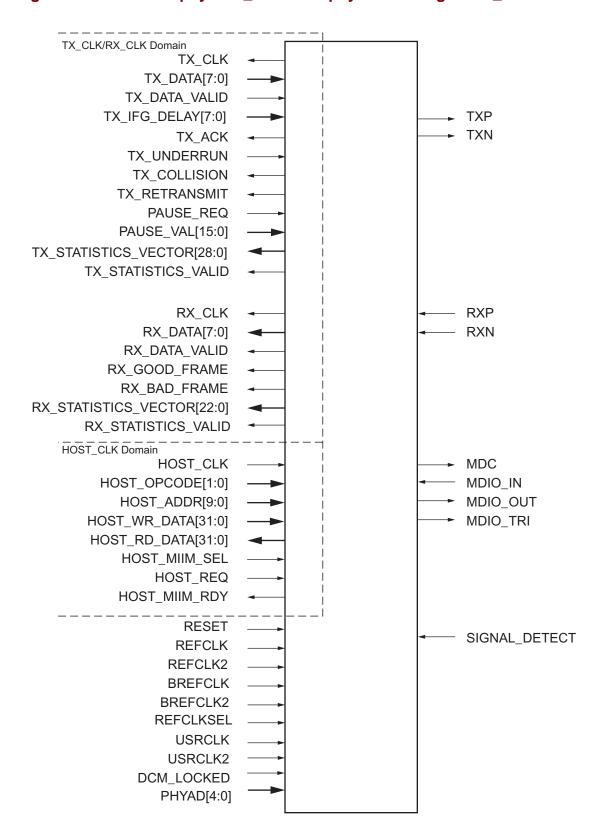

Figure 5: Component Pinout for MAC with PCS and TBI using the optional Management Interface

## Interface Signals for MAC with physical\_interface=tbi and management\_interface=false

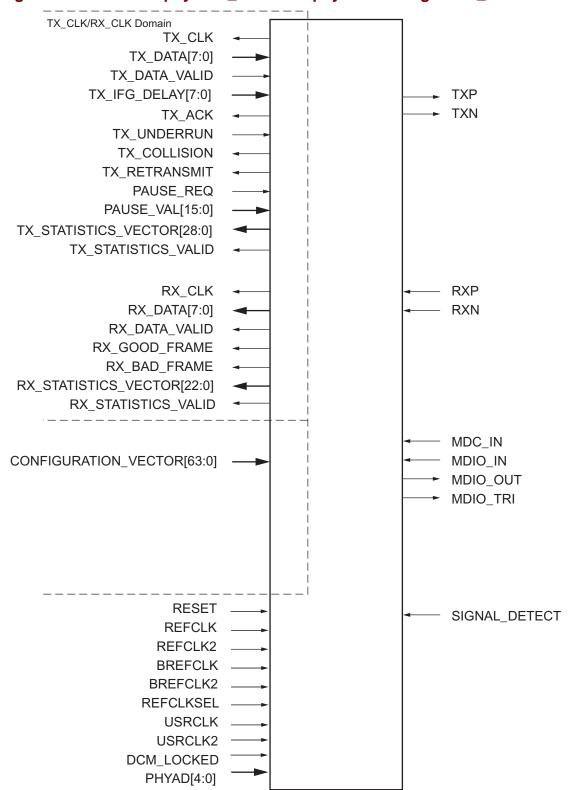

Figure 6: Component Pinout for MAC with PCS and TBI without the optional Management Interface

8

## Interface Signals for MAC with physical\_interface=phy and management\_interface=true

Figure 7: Component Pinout for MAC with PCS & PMA Sublayers using the optional Management Interface

## Interface Signals for MAC with physical\_interface=phy and management\_interface=false

Figure 8: Component Pinout for MAC with PCS & PMA Sublayers without the optional Management Interface

# **Client Side Interface Signal Definition**

Table 3 describes the client-side transmit signals of the MAC core. These signals are used to transmit data from the client to the MAC core.

Table 3: Transmit Client Interface Signal Pins

| Signal                     | Direction | Description                                                                                                                                                                                                           |

|----------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_CLK                     | Output    | Clock for transmit client interface. 125 MHz nominal.                                                                                                                                                                 |

| TX_DATA[7:0]               | Input     | Frame data to be transmitted is supplied on this port.                                                                                                                                                                |

| TX_DATA_VALID              | Input     | Control signal for TX_DATA port.                                                                                                                                                                                      |

| TX_IFG_DELAY[7:0]          | Input     | Control signal for configurable Inter Frame Gap adjustment. See<br>"Transmitter" on page 16 for timing diagrams.                                                                                                      |

| TX_ACK                     | Output    | Handshaking signal. Asserted when the current data on TX_DATA has been accepted. See "Transmitter" on page 16 for timing diagrams.                                                                                    |

| TX_UNDERRUN                | Input     | Asserted by client to force MAC core to corrupt the current frame.                                                                                                                                                    |

| TX_COLLISION               | Output    | Asserted by the MAC core to signal a collision on the medium and that any transmission in progress should be aborted. Always 0 when the MAC core is in full-duplex mode.                                              |

| TX_RETRANSMIT              | Output    | When asserted at the same time as the TX_COLLISION signal, this signals the client that the aborted frame should be resupplied to the MAC core for retransmission. Always 0 when the MAC core is in full-duplex mode. |

| TX_STATISTICS_VECTOR[28:0] | Output    | This gives information on the last frame transmitted. See "Transmitter" on page 16 for vector contents.                                                                                                               |

| TX_STATISTICS_VALID        | Output    | Asserted at end of frame transmission, indicating that the TX_STATISTICS_VECTOR is valid.                                                                                                                             |

#### Notes:

Table 4 describes the client-side receive signals. These signals are used by the MAC core to transfer data to the client.

Table 4: Receive Client Interface Signal Pins

| Signal                     | Direction | Description                                                                                                                    |

|----------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------|

| RX_CLK                     | Output    | Clock for receive client interface. 125 MHz nominal.                                                                           |

| RX_DATA[7:0]               | Output    | Frame data received is supplied on this port.                                                                                  |

| RX_DATA_VALID              | Output    | Control signal for the RX_DATA port.                                                                                           |

| RX_GOOD_FRAME              | Output    | Asserted at end of frame reception to indicate that the frame should be processed by the MAC client. See "Receiver" on page 24 |

| RX_BAD_FRAME               | Output    | Asserted at end of frame reception to indicate that the frame should be discarded by the MAC client. See "Receiver" on page 24 |

| RX_STATISTICS_VECTOR[22:0] | Output    | Provides information about the last frame received. See "Receiver" on page 24 for the vector contents.                         |

| RX_STATISTICS_VALID        | Output    | Asserted at end of frame reception, indicating that the RX_STATISTICS_VECTOR is valid.                                         |

#### Notes:

All signals above are synchronous to RX\_CLK and Active High.

<sup>1.</sup> All the above signals are synchronous to TX\_CLK and Active High.

Table 5 describes the signals used by the client to request a flow control action from the transmit engine. Flow control frames received by the MAC are automatically handled (if the MAC is configured to do so).

Table 5: Flow Control Interface Signal Pinout

| Signal          | Direction | Description                                                                                            |

|-----------------|-----------|--------------------------------------------------------------------------------------------------------|

| PAUSE_REQ       | Input     | Pause request: sends a pause frame down the link. See "Transmitting a PAUSE Control Frame" on page 29. |

| PAUSE_VAL[15:0] | Input     | Pause value: inserted into the parameter field of the transmitted pause frame.                         |

#### Notes:

Table 6 describes the optional signals used by the client to access the management features of the MAC core, including configuration, status, statistics, and MDIO access.

Table 6: Optional Management Interface Signal Pinout (management\_interface=true)

| Signal             | Direction | Description                                                                                                                                                             |

|--------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOST_CLK           | Input     | Clock for management interface. See "Optional Management Interface (management_interface=true)" on page 30 for the signal frequency range.                              |

| HOST_OPCODE[1:0]   | Input     | Defines operation to be performed over MDIO interface. Bit 1 is also used in configuration register access. See "Configuration Registers" on page 30.                   |

| HOST_ADDR[9:0]     | Input     | Address of register to be accessed.                                                                                                                                     |

| HOST_WR_DATA[31:0] | Input     | Data to write to register.                                                                                                                                              |

| HOST_RD_DATA[31:0] | Output    | Data read from register.                                                                                                                                                |

| HOST_MIIM_SEL      | Input     | When asserted, the MDIO interface is accessed. When disasserted, the MAC internal configuration or statistical counter registers are accessed.                          |

| HOST_REQ           | Input     | Used to signal a transaction on the MDIO interface or to read from the statistic registers. See "Optional Management Interface (management_interface=true)" on page 30. |

| HOST_MIIM_RDY      | Output    | When high, the MDIO interface has completed any pending transaction and is ready for a new transaction.                                                                 |

#### Notes:

Table 7 describes the alternative to the optional Management Interface signals. This describes the Configuration Vector which uses direct inputs to the core to replace the functionality of the MAC Configuration bits when the Management Interface is not used..

Table 7: Alternative to the Optional Management Interface: Configuration Vector Signal Pinout (management\_interface=false)

| Signal                     | Direction | Description                                                                                                                                                                                                                |

|----------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONFIGURATION_VECTOR[63:0] | Input     | The Configuration Vector is used to replace the functionality of the MAC Configuration Registers when the Management Interface is not used. See "Optional Configuration Vector (management_interface = false)" on page 38. |

#### Notes:

1. All bits of CONFIGURATION\_VECTOR are registered on input but may be treated as asynchronous inputs.

<sup>1.</sup> These signals are synchronous to TX\_CLK and are Active High.

All signals above are synchronous to HOST\_CLK and are Active High.

Table 8 describes the reset signal.

Table 8: Reset Signal

| Signal | Direction | Description                                                                                                   |

|--------|-----------|---------------------------------------------------------------------------------------------------------------|

| RESET  | Input     | Asynchronous reset for entire core. See "Reset circuit" on page 42 for more information on the reset circuit. |

# **Physical Interface Signal Definition**

Table 9 describes the MDIO (MII Management) interface signals of the MAC core. These signals are typically connected to the MDIO port of a PHY device, either off-chip or an SoC-integrated core. The MDIO format is defined in IEEE802.3 clause 22.

Table 9: MDIO Interface Signal Pinout

| Signal   | Direction | Description                                                                                                                                                                                                                |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDC      | Output    | Management Clock: derived from HOST_CLK on the basis of supplied configuration data when the optional Management Interface is used. See "Optional Management Interface (management_interface=true)" on page 30             |

| MDC_IN   | Input     | When the Optional Management Interface is not used, access to the optional Physical Coding Sublayer (PCS) must be provided by an external MDIO Controller. In this situation the Management Clock is an input to the core. |

| MDIO_IN  | Input     | Input data signal for communication with PHY configuration and status. Tie high if unused.                                                                                                                                 |

| MDIO_OUT | Output    | Output data signal for communication with PHY configuration and status.                                                                                                                                                    |

| MDIO_TRI | Output    | Tristate control for MDIO signals; 0 signals that the value on MDIO_OUT should be asserted onto the MDIO bus.                                                                                                              |

Table 10 describes the optional GMII signals of the MAC core. These are typically attached to a PHY module, either off-chip or internally integrated. The GMII is defined in IEEE802.3 clause 35.

Table 10: Optional GMII Interface Signal Pinout (physical\_interface=gmii)

| Signal        | Direction | Description                                                                                                                                                     |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

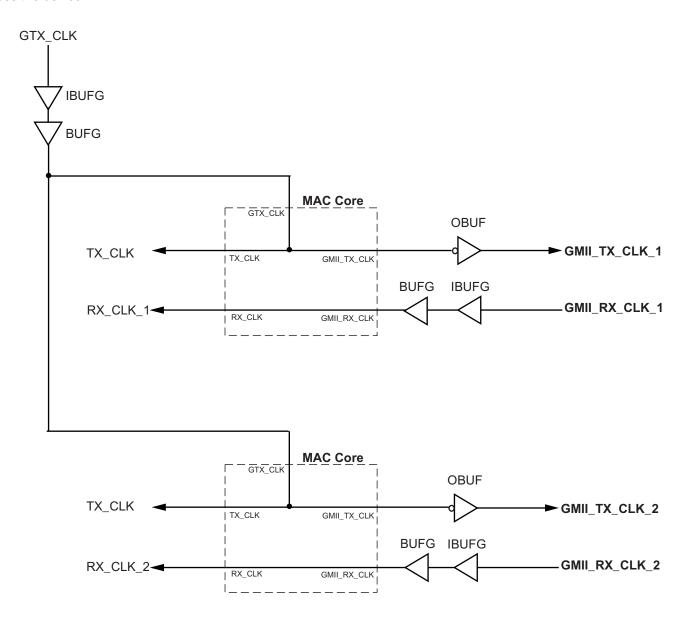

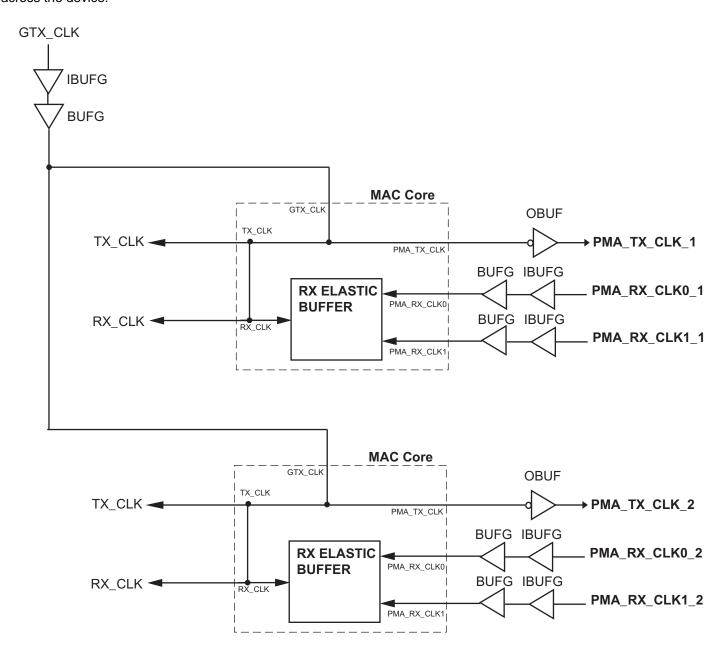

| GTX_CLK       | Input     | Clock signal at 125 MHz. Other transmit clocks are derived from this clock as illustrated in Figure 28. Tolerance must be within IEEE 802.3-2002 specification. |

| GMII_TXD[7:0] | Output    | Transmit data to PHY.                                                                                                                                           |

| GMII_TX_EN    | Output    | Data Enable control signal to PHY.                                                                                                                              |

| GMII_TX_ER    | Output    | Error control signal to PHY.                                                                                                                                    |

| GMII_TX_CLK   | Output    | Clock out to PHY.                                                                                                                                               |

| GMII_CRS      | Input     | Control signal from PHY.                                                                                                                                        |

| GMII_COL      | Input     | Control signal from PHY.                                                                                                                                        |

| GMII_RX_CLK   | Input     | Recovered clock from received data stream by PHY.                                                                                                               |

| GMII_RXD[7:0] | Input     | Received data from PHY.                                                                                                                                         |

| GMII_RX_DV    | Input     | Data Valid control signal from PHY.                                                                                                                             |

| GMII_RX_ER    | Input     | Error control signal from PHY.                                                                                                                                  |

Table 11 describes the TBI (Ten-Bit interface) signals of the MAC core. These are typically attached to a PMA SERDES module. These signals optionally replace the GMII signals described in Table 10 to extend the functionality of the core to include the PCS for 1000BASE-X. The TBI is defined in IEEE802.3 clause 36.

Table 11: Optional TBI Interface Signal Pinout (physical\_interface=tbi)

| Signal              | Direction | Description                                                                                                                                                                                                                                                |

|---------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

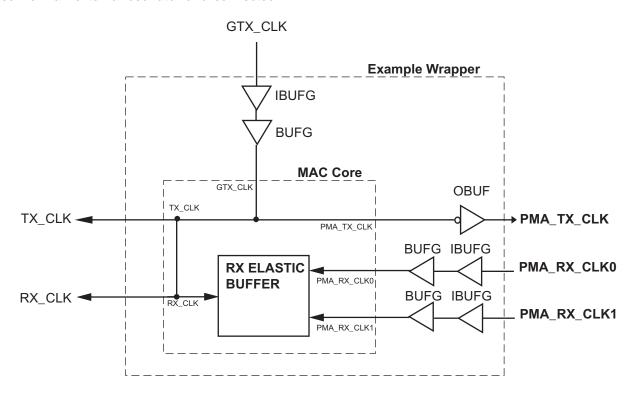

| GTX_CLK             | Input     | Clock signal at 125 MHz. Other transmit clocks will be derived from this clock as illustrated in Figure 32. Tolerance must be within IEEE 802.3-2002 specification.                                                                                        |

| TX_CODE_GROUP[9:0]  | Output    | 10-bit parallel transmit data to PMA Sublayer (SERDES).                                                                                                                                                                                                    |

| PMA_TX_CLK          | Output    | Transmit clock signal to PMA Sublayer (SERDES) at 125MHz.                                                                                                                                                                                                  |

| LOC_REF             | Output    | Causes the PMA sublayer clock recovery unit to lock to PMA_TX_CLK. This signal is tied to Ground.                                                                                                                                                          |

| EWRAP               | Output    | This signal is set from the PCS Control Register 0, bit 14 (loopback). See "PCS Managed Register Block (physical_interface = tbi or phy)" on page 49. When high this instructs the PMA sublayer to electrically loop the transmitter data to the receiver. |

| RX_CODE_GROUP0[9:0] | Input     | 10-bit parallel received data from PMA Sublayer (SERDES); synchronous to PMA_RX_CLK0.                                                                                                                                                                      |

| RX_CODE_GROUP1[9:0] | Input     | 10-bit parallel received data from PMA Sublayer (SERDES); synchronous to PMA_RX_CLK1.                                                                                                                                                                      |

| PMA_RX_CLK0         | Input     | Received clock signal from PMA Sublayer (SERDES) at 62.5MHz.                                                                                                                                                                                               |

| PMA_RX_CLK1         | Input     | Received clock signal from PMA Sublayer (SERDES) at 62.5MHz. This is 180 degrees out of phase with PMA_RX_CLK0.                                                                                                                                            |

| EN_CDET             | Output    | Enables the PMA Sublayer to perform comma realignment; driven from the PCS state machine during the Loss-Of-Sync state.                                                                                                                                    |

| PHYAD[4:0]          | Input     | PHY address of MDIO register set for the PCS.                                                                                                                                                                                                              |

| SIGNAL_DETECT       | Input     | Signal direct from PMD sublayer indicating the presence of light detected at the optical receiver. If driven high, this indicates that the optical receiver has detected light. If driven low this indicates the absence of light.                         |

|                     |           | If unused, tie high to enable the operation the core.                                                                                                                                                                                                      |

#### Notes:

PHYAD and SIGNAL\_DETECT are asynchronous inputs. SIGNAL\_DETECT is Active High.

Table 12 describes the interface signals for the Optional PCS/PMA sublayer of the MAC core. These signals optionally replace the GMII signals described in Table 10 to extend the functionality of the core to include the PCS and PMA sublayers for 1000BASE-X. This option uses the Virtex-II Pro Rocket I/O functionality which is integrated into the core. The PMA sublayer for 1000BASE-X is defined in IEEE802.3 clause 36.

Table 12: Optional PCS/PMA sublayer Interface Signal Pinout (physical\_interface=phy)

| Signal        | Direction | Description                                                                                                                                                                                                                                        |

|---------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFCLK        | Input     | High Quality Reference clock for Multi-Gigabit Transceivers (62.5 MHz). See Rocket I/O User Guide.                                                                                                                                                 |

| REFCLK2       | Input     | Alternative High Quality Reference clock for Multi-Gigabit Transceivers (62.5 MHz). See Rocket I/O User Guide.                                                                                                                                     |

| BREFCLK       | Input     | Alternative High Quality Reference clock for Multi-Gigabit Transceivers (62.5 MHz). This optionally replaces REFCLK. See Rocket I/O User Guide.                                                                                                    |

| BREFCLK2      | Input     | Alternative High Quality Reference clock for Multi-Gigabit Transceivers (62.5 MHz). This optionally replaces REFCLK2. See Rocket I/O User Guide.                                                                                                   |

| REFCLKSEL     | Input     | Selects between either (B)REFCLK or (B)REFCLK2 as the input clock source to the MGT. See Rocket I/O User Guide.                                                                                                                                    |

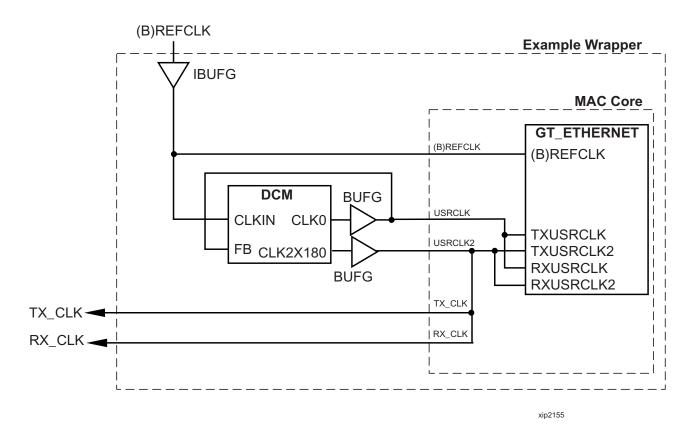

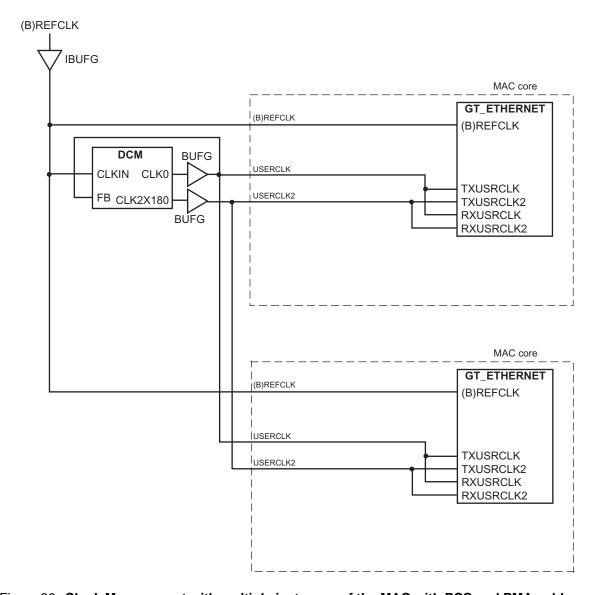

| USERCLK       | Input     | Clock signal at 62.5 MHz. This is connected to the TXUSRCLK and RXUSRCLK ports of the Rocket I/O MGT. This may be derived from (B)REFCLK using a DCM as illustrated in Figure 35.                                                                  |

| USERCLK2      | Input     | Clock signal at 125 MHz. This is connected to the TXUSRCLK2 and RXUSRCLK2 ports of the Rocket I/O MGT. This may be derived from (B)REFCLK using a DCM as illustrated in Figure 35.                                                                 |

| DCM_LOCKED    | Input     | If a DCM is used to derive USRCLK and USRCLK2 as illustrated in Figure 35, the LOCKED port of the DCM must be connected to the DCM_LOCKED port of the core. The core will hold it's Rocket I/O MGT in reset until DCM_LOCKED is driven to logic 1. |

| TXP/TXN       | Output    | Differential pair for serial transmission from PMA to PMD. The clock is embedded in the data stream.                                                                                                                                               |

| RXP/RXN       | Input     | Differential pair for serial reception from PMD to PMA. The clock is extracted from the data stream.                                                                                                                                               |

| PHYAD[4:0]    | Input     | PHY address of MDIO register set for the PCS.                                                                                                                                                                                                      |

| SIGNAL_DETECT | Input     | Signal direct from PMD sublayer indicating the presence of light detected at the optical receiver. If driven high, this indicates that the optical receiver has detected light. If driven low this indicates the absence of light.                 |

|               |           | If unused, tie high to enable the operation the core.                                                                                                                                                                                              |

#### Notes:

1. PHYAD and SIGNAL\_DETECT are asynchronous inputs. SIGNAL\_DETECT is Active High.

# **Functional Description**

#### **Client Interface**

The client interface is designed for maximum flexibility in matching to a client switching fabric or network processor interface.

The data pathway is 8 bits wide in both the transmit and receive directions, with each pathway synchronous to the TX\_CLK and RX\_CLK respectively for completely independent full duplex operation.

#### **Transmitter**

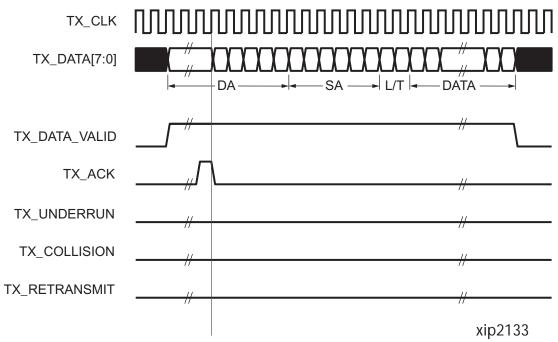

#### Normal Frame Transmission

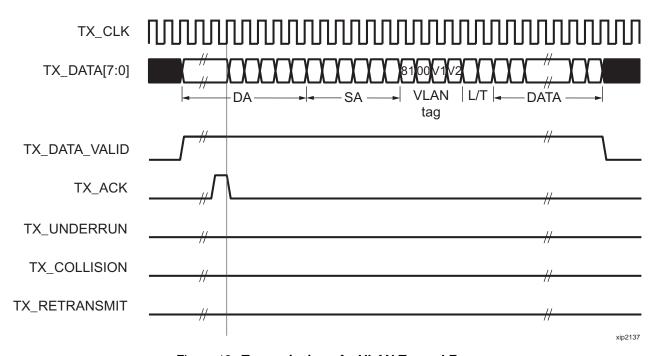

The timing of a normal outbound frame transfer can be seen in Figure 9. When the client wants to transmit a frame, it places the first column of data onto the TX\_DATA port and asserts a "1" onto TX\_DATA\_VALID.

When the MAC core has read this first byte of data, it will assert the TX\_ACK signal; on the next and subsequent rising clock edges, the client must provide the remainder of the data for the frame.

The end of frame is signalled to the MAC core by taking TX DATA VALID Low.

## In-Band Parameter Encoding

For maximum flexibility in switching applications, the Ethernet frame parameters (destination address, source address, length/type and optionally FCS) are encoded within the same data stream that the frame payload is transferred upon, rather than on separate ports. This is illustrated in the timing diagrams. Definitions of the abbreviations used in the timing diagrams are described in Table 13.

Table 13: Abbreviations Used in Timing Diagrams

| Abbreviation | Definition                    |

|--------------|-------------------------------|

| DA           | Destination Address; 6 bytes  |

| SA           | Source Address; 6 bytes       |

| L/T          | Length/Type Field; 2 bytes    |

| FCS          | Frame Check Sequence; 4 bytes |

Figure 9: Normal Frame Transmission Across Client Interface

#### **Padding**

When fewer than 46 bytes of data are supplied by the client to the MAC core, the transmitter module will add padding up to the minimum frame length. The exception to this is when the MAC core is configured for client-passed FCS; in this case the client must also supply the padding to maintain the minimum frame length (see Client-Supplied FCS Passing).

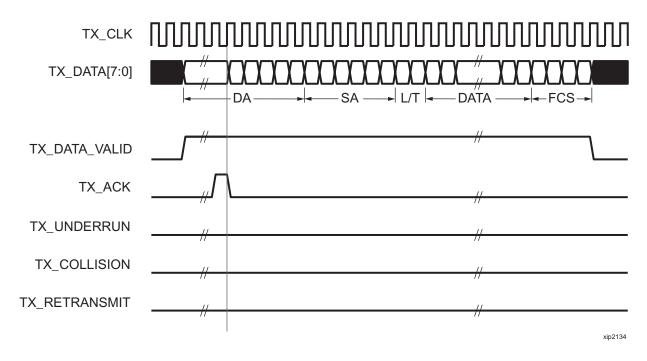

## Client-Supplied FCS Passing

If the MAC core is configured to have the FCS field passed in by the client (see "Configuration Registers" on page 30), the transmission timing is as depicted in Figure 10. In this case, it is the responsibility of the client to ensure that the frame meets the Ethernet minimum frame length requirements; the MAC core will not perform any padding of the payload.

Figure 10: Frame Transmission with Client-supplied FCS

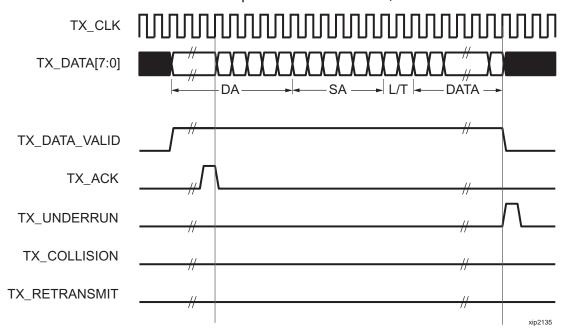

#### Client Underrun

The timing of an aborted transfer can be seen in Figure 11. This may happen, for instance, if a FIFO connected to the client interface empties before a frame is completed. When the client asserts TX\_UNDERRUN during a frame transmission, the MAC core will insert an error code to corrupt the

current frame, and then fall back to idle transmission. It is the responsibility of the client to re-queue the aborted frame for transmission.

When an underrun occurs, TX\_DATA\_VALID may be asserted on the clock cycle after the TX\_UNDERRUN assertion to request a new transmission.

Figure 11: Frame Transmission with Underrun

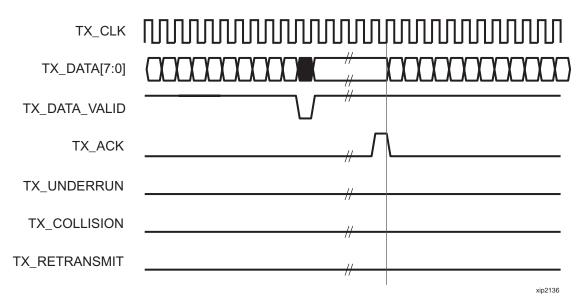

#### Back-to-Back Transfers

Figure 12 shows the case where the MAC client is immediately ready to transmit a second frame of data following completion of its first frame. In this figure, the end of the first frame is shown on the left. On the clock cycle immediately following the final byte of the first frame, TX\_DATA\_VALID is taken low by the client, and is taken high one clock cycle later to indicate that the first byte of the destination address of the second frame is on TX\_DATA awaiting transmission.

When the MAC core is ready to accept data, TX\_ACK is asserted and the transmission continues in the same manner as in the case of the single frame. The MAC core will defer the assertion of TX\_ACK appropriately to comply with inter-packet gap requirements and flow control requests.

If the MAC core is operating in half-duplex mode, the timing shown in Figure 12 is required to take advantage of frame bursting; the MAC core is only guaranteed to retain control of the medium if the TX\_DATA\_VALID signal is low for a single clock cycle. For more information on frame bursting, see IEEE 802.3-2002.

Figure 12: Back to Back Frame Transmission

## **VLAN Tagged Frames**

Transmission of a VLAN tagged frame (if enabled) can be seen in Figure 13. Note that the handshaking signals across the interface do not change; however, the VLAN type tag 81-00 must be supplied by the client to signify that

the frame is VLAN tagged. The client also supplies the two bytes of Tag Control Information, V1 and V2, at the appropriate times in the data stream. More information on the contents of these two bytes can be found in IEEE 802.3-2002.

Figure 13: Transmission of a VLAN Tagged Frame

#### Maximum Permitted Frame Length

The maximum legal length of a frame specified in IEEE 802.3-2002 is 1518 bytes for non-VLAN tagged frames. VLAN tagged frames may be extended to 1522 bytes. When jumbo frame handling is disabled and the client attempts to transmit a frame which exceeds the maximum legal length, the MAC core will insert an error code to cor-

rupt the current frame and the frame will be truncated to the maximum legal length. When jumbo frame handling is enabled, frames which are longer than the legal maximum are transmitted error-free.

For more information on enabling and disabling jumbo frame handling, see "Configuration Registers" on page 30.

## Frame Collisions - Half Duplex Operation Only

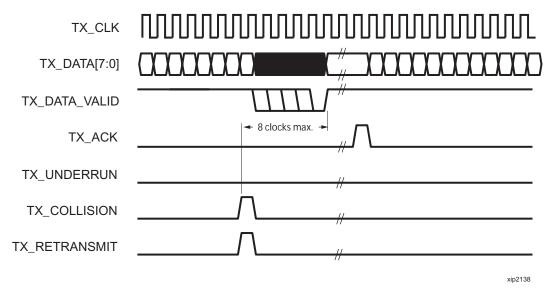

In half duplex Ethernet operation, collisions will occur on the medium as a matter of course; this is how the arbitration algorithm is fulfilled. In case of a collision, the MAC core signals to the client that data may need to be resupplied as follows.

If there is a collision, the TX\_COLLISION signal will be set to "1" by the MAC core. If a frame is in progress, the client must abort the transfer and take TX\_DATA\_VALID to "0."

If the TX\_RETRANSMIT signal is "1" in the same clock cycle that the TX\_COLLISION signal is "1," the client must

resubmit the previous frame to the MAC core for retransmission; TX\_DATA\_VALID must be asserted to the MAC core within 8 clock cycles of the TX\_COLLISION signal in order to meet Ethernet timing requirements. See Figure 14.

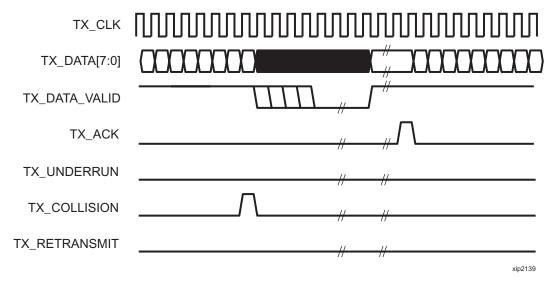

If the TX\_RETRANSMIT signal is "0" in the same clock cycle that the TX\_COLLISION signal is "1," the number of retries for this frame has exceeded the Ethernet specification and the frame should be dropped by the client. The client can then make any new frame available to the MAC for transmission without timing restriction. See Figure 15.

Figure 14: Collision Handling - Frame retransmission required

Figure 15: Collision Handling - No frame retransmission required

## Interframe Gap Adjustment

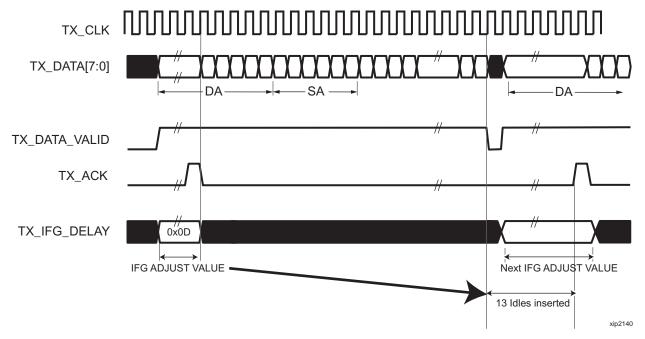

The user can elect to vary the length of the inter fame gap. If this function is selected (via a configuration bit in the transmitter control register, see "Configuration Registers" on page 30) then the MAC will exert back pressure to delay the transmission of the next frame until the requested number of Idle cycles has elapsed. The number of Idle cycles is controlled by the value on the TX\_IFG\_DELAY port at the start of frame transmission; Figure 16 shows the MAC operating in this mode.

Reducing the Inter fame gap to below the IEEE 802.3-2002 minimum of 12 Idles is supported in Full Duplex only designs and will transmit an absolute minimum of 4 Idles. If the Interframe gap adjustment is reduced below 12 Idles, then the accuracy of the Optional Statistical Gathering (statistics gathering=true) Counters cannot be guaranteed. TX\_STATISTIC\_VECTOR However, the RX\_STATISTIC\_VECTOR will always remain correct.

Figure 16: Interframe Gap Adjustment

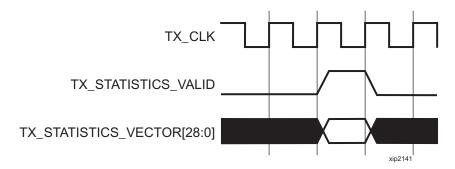

#### Transmitter Statistics Vector

The statistics for the frame transmitted are contained within the TX STATISTICS VECTOR. The vector is driven synchronously by the transmitter clock, TX CLK, following frame transmission. The bit field definition for the Vector is defined in Table 14.

All bit fields, with the exception of BYTE\_VALID are valid only when the TX STATISTICS VALID is asserted. This is illustrated in Figure 17. BYTE\_VALID is significant on every TX CLK cycle.

TX\_STATISTICS\_VECTOR bits 25 down to 17 inclusive are for half duplex only and will be set to logic 0 when operating in full duplex mode.

Figure 17: Transmitter Statistics Vector Timing

Table 14: Bit Definition for the Transmitter Statistics Vector

| TX_STATISTICS_VECTOR | Name                    | Description                                                                                                                                                                           |

|----------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28                   | PAUSE_FRAME_TRANSMITTED | Asserted if the previous frame was a pause frame that the MAC itself initiated in response to a PAUSE_REQ assertion.                                                                  |

| 27                   | BYTE_VALID              | Asserted if a MAC frame byte (DA to FCS inclusive) is in the process of being transmitted. This is valid on every clock cycle.                                                        |

|                      |                         | Do not use this as an enable signal to indicate that data is present on GMII_TXD[7:0].                                                                                                |

| 26                   | Reserved                | Returns logic 0.                                                                                                                                                                      |

| 25 down to 22        | TX_ATTEMPTS[3:0]        | The number of attempts that have been made to transmit the previous frame. This is a 4-bit number: 0 should be interpreted as 1 attempt; 1 as 2 attempts, up until 15 as 16 attempts. |

| 21                   | Reserved                | Returns logic 0.                                                                                                                                                                      |

| 20                   | EXCESSIVE_COLLISION     | Asserted if a collision has been detected on each of the last 16 attempts to transmit the previous frame.                                                                             |

| 19                   | LATE_COLLISION          | Asserted if a late collision occurred during frame transmission.                                                                                                                      |

| 18                   | EXCESSIVE_DEFERRAL      | Asserted if the previous frame was deferred for an excessive amount of time as defined by the constant "maxDeferTime" in IEEE 802.3-2002.                                             |

| 17                   | TX_DEFERRED             | Asserted if transmission of the frame was deferred.                                                                                                                                   |

| 16                   | VLAN_FRAME              | Asserted if the previous frame contained a VLAN identifier in the Length/Type field when transmitter VLAN operation is enabled.                                                       |

| 15 down to 5         | FRAME_LENGTH_COUNT      | The length of the previous frame in number of bytes. The count will stick at 2047 for any Jumbo frames larger than this value.                                                        |

| 4                    | CONTROL_FRAME           | Asserted if the previous frame had the special MAC Control Type code 88-08 in the Length/Type field.                                                                                  |

| 3                    | UNDERRUN_FRAME          | Asserted if the previous frame contained an underrun error.                                                                                                                           |

| 2                    | MULTICAST_FRAME         | Asserted if the previous frame contained a multicast address in the Destination Address field.                                                                                        |

| 1                    | BROADCAST_FRAME         | Asserted if the previous frame contained a broadcast address in the Destination Address field.                                                                                        |

| 0                    | SUCCESSFUL_FRAME        | Asserted if the previous frame was transmitted without error.                                                                                                                         |

#### Receiver

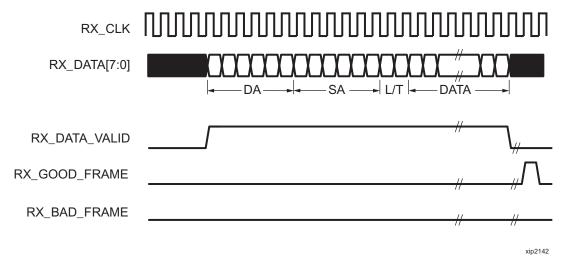

## Normal Frame Reception

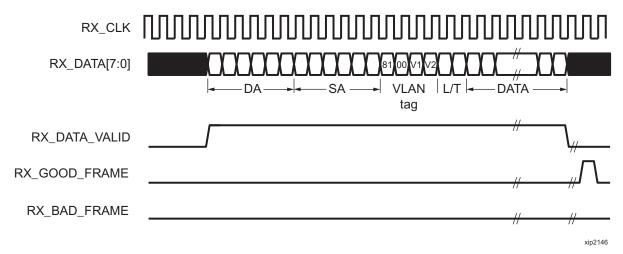

The timing of a normal inbound frame transfer can be seen in Figure 18. The client must be prepared to accept data at any time; there is no buffering within the MAC to allow for latency in the receive client. Once frame reception begins,

data is transferred on consecutive clock cycles to the receive client until the frame is complete. The MAC asserts the RX\_GOOD\_FRAME signal to indicate that the frame was successfully received and that the frame should be analyzed by the client.

Figure 18: Normal Frame Reception

Frame parameters (destination address, source address, length/type and optionally FCS) are supplied on the data bus according to the timing diagram. The abbreviations are the same as those described in Table 13 on page 16.

If the Length/Type field in the frame has the Length interpretation, and this indicates that the inbound frame has been padded to meet the Ethernet minimum frame size specification, then this padding will not be passed to the client in the data payload. The exception to this is in the case where FCS passing is enabled, see "Client-Supplied FCS Passing" on page 25.

Therefore, when Client-Supplied FCS passing is disabled, RX\_DATA\_VALID = '0' between frames for the duration of the Padding field (if present), the FCS field, carrier extension (if present), the interframe gap following the frame, and the preamble field of the next frame. When Client-Supplied

FCS passing is enabled, RX\_DATA\_VALID = '0' between frames for the duration of carrier extension (if present), the interframe gap, and the preamble field of the following frame.

#### RX GOOD FRAME, RX BAD FRAME timing

Although the timing diagram in Figure 18 shows the RX\_GOOD\_FRAME signal asserted shortly after the last valid data on RX\_DATA, this is not always the case. The RX\_GOOD\_FRAME or RX\_BAD\_FRAME signals are asserted only after all frame checks are completed. This is after the FCS field has been received (and after reception of carrier extension, if present).

Therefore, either RX\_GOOD\_FRAME or RX\_BAD\_FRAME is asserted following frame reception at the beginning of the interframe gap.

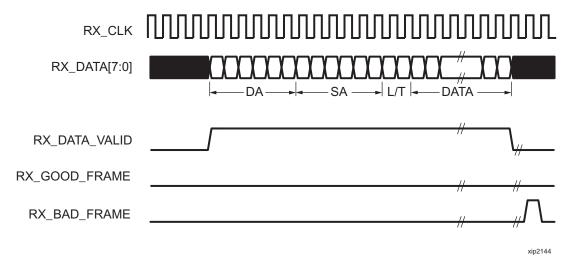

## Frame Reception with Errors

The case of an unsuccessful frame reception (for example, a fragment frame or a frame with an incorrect FCS) can be seen in Figure 19. In this case, the RX\_BAD\_FRAME signal

is asserted to the client at the end of the frame. It is then the responsibility of the client to drop the data already transferred for this frame.

Figure 19: Frame Reception with Error

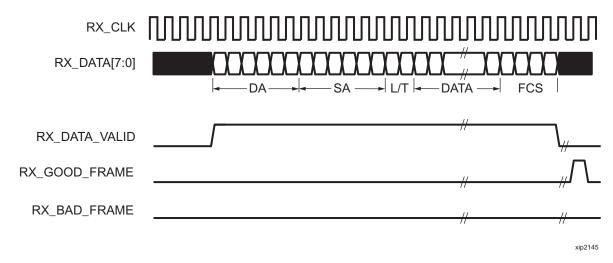

## Client-Supplied FCS Passing

If the MAC core is configured to pass the FCS field to the client (see "Configuration Registers" on page 30), then this is handled as shown in Figure 20.

In this case, any padding inserted into the frame to meet Ethernet minimum frame length specifications will be left intact and passed to the client.

Note that even though the FCS is passed up to the client, it is also verified by the MAC core, and RX\_BAD\_FRAME asserted if the FCS check fails.

25

Figure 20: Frame Reception with In-Band FCS Field

## **VLAN Tagged Frames**

The reception of a VLAN tagged frame (if enabled) can be seen in Figure 21. The VLAN frame is passed to the client so that the frame may be identified as VLAN tagged; this is

followed by the Tag Control Information bytes, V1 and V2. More information on the interpretation of these bytes may be found in IEEE 802.3-2002 standard.

Figure 21: Reception of a VLAN Tagged Frame

# Maximum Permitted Frame Length

The maximum legal length of a frame specified in IEEE 802.3-2002 is 1518 bytes for non-VLAN tagged frames. VLAN tagged frames may be extended to 1522 bytes. When jumbo frame handling is disabled and the core receives a frame which exceeds the maximum legal length, RX\_BAD\_FRAME will be asserted. When jumbo frame handling is enabled, frames which are longer than the legal maximum are received in the same way as shorter frames.

For more information on enabling and disabling jumbo frame handling, see "Configuration Registers" on page 30.

#### Length/Type Field Error Checks

## **Enabled**

26

Default operation is with the Length/Type error checking enabled (see "Receiver Configuration Word 1" on page 31). In this mode the following checks are made on all frames received. If either of these checks fail then the frame is marked as BAD.

A value in the Length/Type field that is greater than or equal to decimal 46 but less than decimal 1536 (a Length interpretation) is checked against the actual data length received.  A value in the Length/Type field that is less than decimal 46 is checked to see that the data field is padded to exactly 46 bytes (so that the resultant frame is minimum frame size: 64 bytes total in length).

Furthermore, if Padding is indicated (the Length/Type field is less than decimal 46) and Client-Supplied FCS Passing is disabled, then the Length value in the Length/Type field will be used to deassert RX\_DATA\_VALID after the indicated number of data bytes so that the Padding bytes are removed from the frame.

#### **Disabled**

When the Length/Type error checking is disabled (see "Receiver Configuration Word 1" on page 31) the Length/Type error checks described above are not performed. A frame containing only these errors will be marked as GOOD.

Furthermore, if Padding is indicated and Client-Supplied FCS Passing is disabled, then a Length Value in the Length/Type field will not be used to deassert RX\_DATA\_VALID. Instead RX\_DATA\_VALID will be deasserted before the start of the FCS field; in this way any padding will not be removed from the frame.

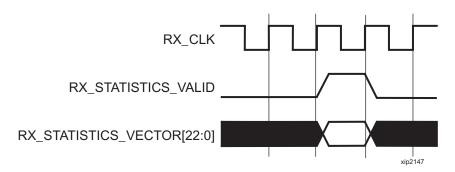

#### Receiver Statistics Vector

The statistics for the frame received are contained within the RX\_STATISTICS\_VECTOR. The vector is driven synchronously by the receiver clock, RX\_CLK following frame reception. The bit field definition for the Vector is defined in Table 15.

All bit fields, with the exception of BYTE\_VALID are valid only when the RX\_STATISTICS\_VALID is asserted. This is illustrated in Figure 22. BYTE\_VALID is significant on every RX\_CLK cycle.

Figure 22: Receiver Statistics Vector Timing

Table 15: Bit Definition for the Receiver Statistics Vector

| RX_STATISTICS_VECTOR | Name                     | Description                                                                                                                                                                                                                                                                                                                     |

|----------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22                   | LENGTH/TYPE Out of Range | Asserted if the length/type field contained a length value that did not match the number of MAC client data bytes received. Also high if the length/type field indicated that the frame contained padding but the number of MAC client data bytes received was not equal to 64 bytes (minimum frame size).                      |

|                      |                          | The exception to the above is when the Length/Type Field Error Checks are disabled, in which case this bit will not be asserted.                                                                                                                                                                                                |

| 21                   | BAD_OPCODE               | Asserted if the previous frame was error-free and contained the special Control Frame identifier in the Length/Type field, but contained an opcode that is unsupported by the MAC (Any Opcode other than PAUSE).                                                                                                                |

| 20                   | FLOW_CONTROL_FRAME       | Asserted if the previous frame was error-free, contained the special Control Frame identifier in the Length/Type field, contained a Destination Address that matched either the MAC Control Multicast Address or the configured source address of the MAC, contained the supported PAUSE opcode, and was acted upon by the MAC. |

| 19                   | BYTE_VALID               | Asserted if a MAC frame byte (DA to FCS inclusive) is in the process of being received. This is valid on every clock cycle.                                                                                                                                                                                                     |

|                      |                          | Do not use this as an enable signal to indicate that data is present on RX_DATA[7:0].                                                                                                                                                                                                                                           |

| 18                   | VLAN_FRAME               | Asserted if the previous frame contained a VLAN identifier in the Length/Type field when receiver VLAN operation is enabled.                                                                                                                                                                                                    |

Table 15: Bit Definition for the Receiver Statistics Vector

| RX_STATISTICS_VECTOR | Name                    | Description                                                                                                                                                                                   |

|----------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                   | OUT_OF_BOUNDS           | Asserted if the previous frame exceeded the specified IEEE802.3-2002 maximum legal length (see "Maximum Permitted Frame Length" on page 26). This is only valid if Jumbo frames are disabled. |

| 16                   | CONTROL_FRAME           | Asserted if the previous frame contained the special Control Frame identifier in the Length/Type field.                                                                                       |

| 15 down to 5         | FRAME_LENGTH_COUNT      | The length of the previous frame in number of bytes. The count will stick at 2047 for any Jumbo frames larger than this value.                                                                |

| 4                    | MULTICAST_FRAME         | Asserted if the previous frame contained a multicast address in the Destination Address field.                                                                                                |

| 3                    | BROADCAST_FRAME         | Asserted if the previous frame contained the broadcast address in the Destination Address field.                                                                                              |

| 2                    | FCS_ERROR               | Asserted if the previous frame received had an incorrect FCS value or the MAC detected error codes during frame reception.                                                                    |

| 1                    | BAD_FRAME <sup>1</sup>  | Asserted if the previous frame received contained errors.                                                                                                                                     |

| 0                    | GOOD_FRAME <sup>1</sup> | Asserted if the previous frame received was error-free.                                                                                                                                       |

<sup>1.</sup> If the Length/Type Field Error Checks are disabled then a frame which contains this type of error will be marked as a GOOD\_FRAME providing no additional errors were detected.

#### **Flow Control**

The flow control block is designed to Clause 31 of the IEEE 802.3-2002 standard. The MAC may be configured to send pause frames and to act upon their reception. These two behaviors can be configured asymmetrically; see "Configuration Registers" on page 30.

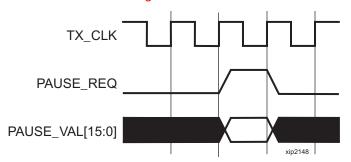

# Transmitting a PAUSE Control Frame

The client initiates a flow control frame by asserting PAUSE\_REQ while the pause value is on the PAUSE\_VAL bus. These signals are synchronous to TX\_CLK. The timing of this can be seen in Figure 23.

Figure 23: Pause Request Timing

If the MAC core is configured to support transmit flow control, this action causes the core to transmit a PAUSE control frame on the link, with the PAUSE parameter set to the value on PAUSE\_VAL in the cycle when PAUSE\_REQ was asserted. This will not disrupt any frame transmission in progress but will take priority over any pending frame trans-

mission. This frame will be transmitted even if the transmitter is in the paused state itself.

## Receiving a Pause Control Frame

When an error-free frame is received by the MAC core, the following checks are made:

- The Destination Address field is matched against the MAC Control Multicast address or the configured Source Address for the MAC (see "Configuration Registers" on page 30).

- 2. The Length/Type field is matched against the MAC Control Type code.

- 3. The opcode field contents are matched against the PAUSE opcode if check 2 is true.

If any of the above checks are false or the MAC Flow Control logic for the receiver is disabled, the frame is ignored by the Flow Control logic and passed up to the client.

If the frame passes all of the above checks, is of minimum legal size and the MAC Flow Control logic for the receiver is enabled, the pause value parameter in the frame is then used to inhibit transmitter operation for the time defined in the IEEE802.3-2002 specification. This inhibit is implemented using the same back pressure scheme shown in Figure 12. Because the received pause frame has been acted upon, it is passed to the client with RX\_BAD\_FRAME asserted to indicate to the client that it should be dropped.

Reception of any frame for which check 2 is true and which is not of legal minimum length is considered an invalid Control frame. This will be ignored by the Flow Control logic and passed to the client with RX\_BAD\_FRAME asserted.

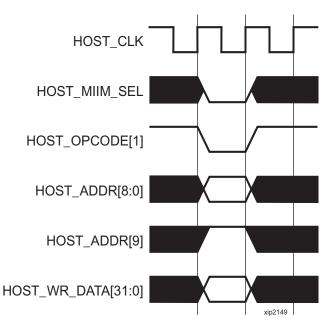

# Optional Management Interface (management\_interface=true)

The management interface is a processor-independent interface with standard address, data and control signals. It may be used as is, or a wrapper may be applied (not supplied) to interface to common bus architectures.

This interface is used for:

- · Configuration of the MAC core;

- Access to optional statistics counters for use by higher layers, for example, SNMP

- access through the MDIO interface to the management registers located in the PHY attached to the MAC core.

The management interface is accessed differently depending on the type of transaction; a truth table showing which access method is required for each transaction type is shown in Table 16. These access methods are described in the following sections.

Table 16: Management Interface Transaction Types

| Transaction   | HOST_MIIM_SEL | HOST_ADDR[9] |

|---------------|---------------|--------------|

| Configuration | 0             | 1            |

| Statistics    | 0             | 0            |

| MIIM access   | 1             | X            |

## **HOST\_CLK Frequency**

The management interface clock, HOST\_CLK, is used to derive the MDIO clock, MDC, and is therefore subject to some frequency restrictions. This HOST\_CLK must be:

≥ 10 MHz

≤ 100 MHz

Configuring the MAC core to derive the MDC signal from this clock is detailed in "MDIO Interface" on page 37.

## **Configuration Registers**

After power up or reset, the client may reconfigure the core parameters from their defaults, such as flow control support. Configuration changes can be written at any time. Both the receiver and transmitter logic will only respond to configuration changes during Inter Frame Gaps. The exceptions to this are the configurable resets which take effect immediately.

Configuration of the MAC core is performed through a register bank accessed through the management interface. The configuration registers available in the core are detailed in Table 17. As can be seen, the address has some implicit don't care bits; any access to an address in the ranges shown will perform a 32-bit read or write from the same configuration word.

Table 17: Configuration Registers

| Address     | Description                      |

|-------------|----------------------------------|

| 0x200-0x23F | Receiver Configuration (Word 0). |

| 0x240-0x27F | Receiver Configuration (Word 1). |

| 0x280-0x2BF | Transmitter Configuration.       |

| 0x2C0-0x2FF | Flow Control Configuration.      |

| 0x300-0x33F | Reserved.                        |

| 0x340-0x37F | Management Configuration.        |

The register contents for the two receiver configuration words can be seen in Table 18 and Table 19.

Table 18: Receiver Configuration Word 0

| Bit  | Default Value | Description                                                                                                                                                                                                                                                    |

|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-0 | All 0's       | Pause frame MAC Source Address[31:0]. This address is used by the MAC to match against the Destination Address of any incoming flow control frames. It is also used by the flow control block as the Source Address (SA) for any outbound flow control frames. |

|      | 741100        | The address is ordered so the first byte transmitted/received is the lowest positioned byte in the register; for example, a MAC address of AA-BB-CC-DD-EE-FF would be stored in Address[47:0] as 0xFFEEDDCCBBAA.                                               |

#### Table 19: Receiver Configuration Word 1

| Bit   | Default Value | Description                                                                                                                                                                                                                                                                                   |

|-------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-0  | All 0's       | Pause frame MAC Source Address[47:32]. See description in Table 18.                                                                                                                                                                                                                           |

| 24-16 | N/A           | Reserved.                                                                                                                                                                                                                                                                                     |

| 25    | 0             | Length/Type Error Check Disable. When this bit is set to "1", the core will not perform the Length/Type field error checks as described in "Length/Type Field Error Checks" on page 26. When this bit is set to "0" the Length/Type field checks will be performed: this is normal operation. |

| 26    | 0             | Half Duplex. If "1," the receiver will operate in half duplex mode. If "0," the receiver will operate in full duplex mode. Has no effect if XCO parameter half_duplex_capable = false.                                                                                                        |

| 27    | 0             | VLAN Enable. When this bit is set to "1," VLAN tagged frames will be accepted by the receiver.                                                                                                                                                                                                |

| 28    | 1             | Receiver Enable. If set to "1," the receiver block will be operational. If set to "0," the block will ignore activity on the physical interface RX port.                                                                                                                                      |

| 29    | 0             | In-band FCS Enable. When this bit is "1," the MAC receiver will pass the FCS field up to the client as described in "Client-Supplied FCS Passing" on page 25. When it is "0," the client will not be passed the FCS. In both cases, the FCS will be verified on the frame.                    |

| 30    | 0             | Jumbo Frame Enable. When this bit is set to "1," the MAC receiver will accept frames over the specified IEEE802.3-2002 maximum legal length. When this bit is "0," the MAC will only accept frames up to the specified maximum.                                                               |

| 31    | 0             | Reset. When this bit is set to "1," the receiver will be reset. The bit will then automatically revert to "0." Note that this reset will also set all of the receiver configuration registers to their default values.                                                                        |

#### Notes:

1. In changing the receiver's mode from Half Duplex to Full Duplex, there is a period of time of up to 2.4 us following the mode change when no new receiver statistics can be stored in the optional Statistical Counters.

The register contents for the Transmitter Configuration Word are described in Table 20.

Table 20: Transmitter Configuration Word

| Bit  | Default Value | Description                                                                                                                                                                                                                                                                                                                                                            |

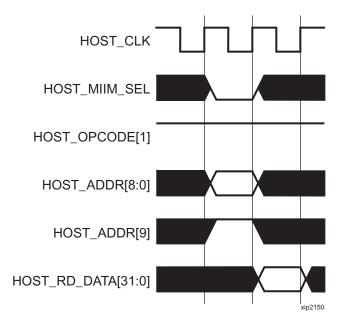

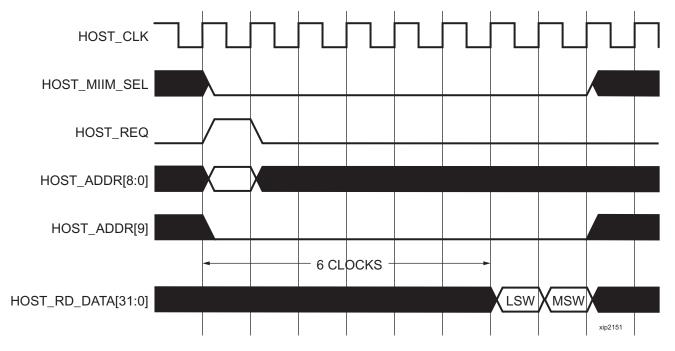

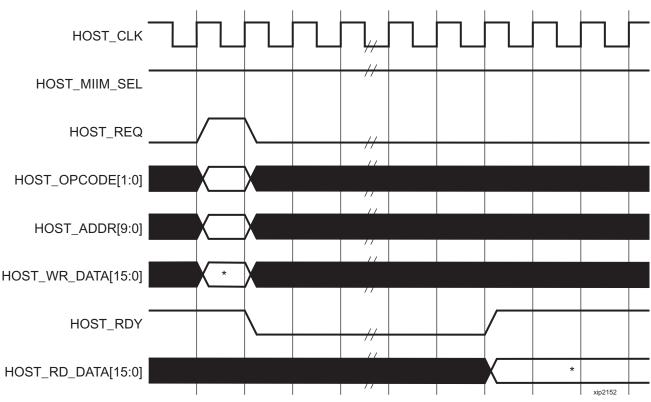

|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|